# Solid State Electronic Devices

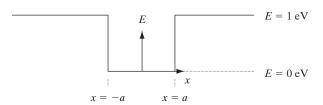

SEVENTH EDITION

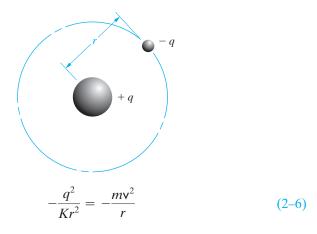

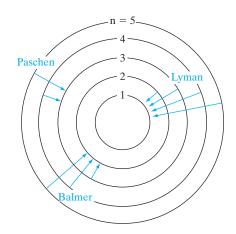

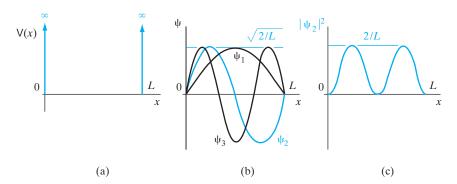

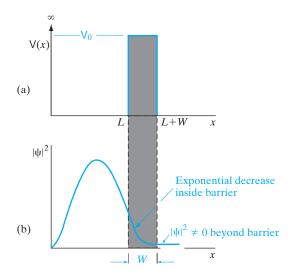

Ben G. Streetman • Sanjay Kumar Banerjee

**PEARSON**

### **Solid State Electronic Devices**

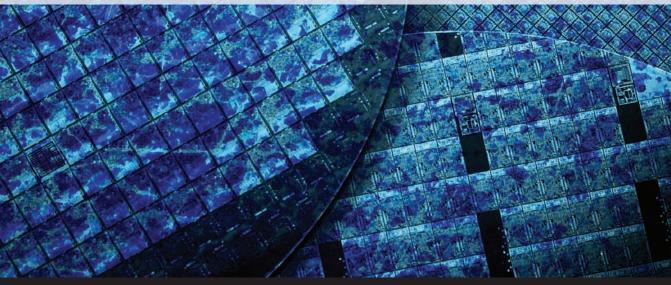

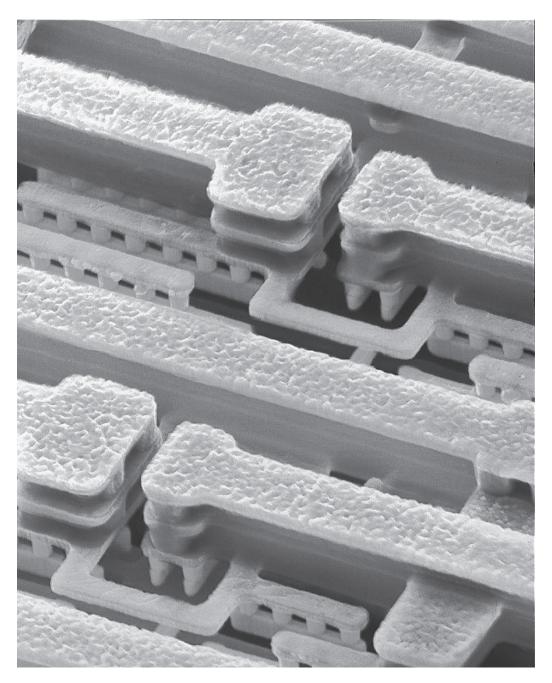

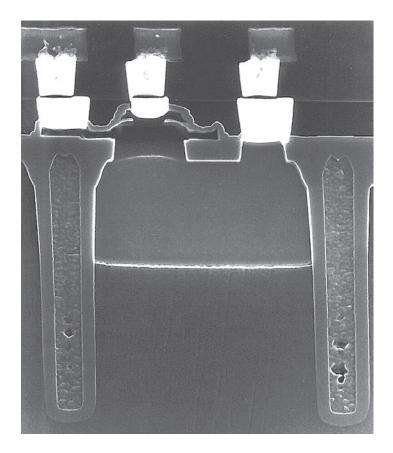

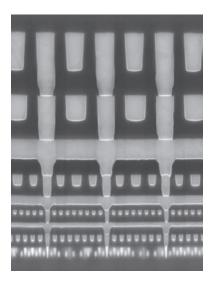

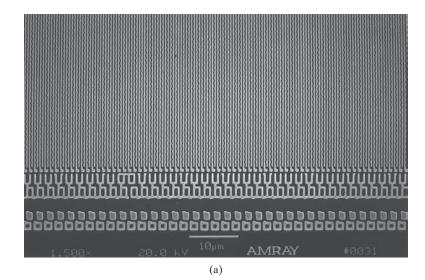

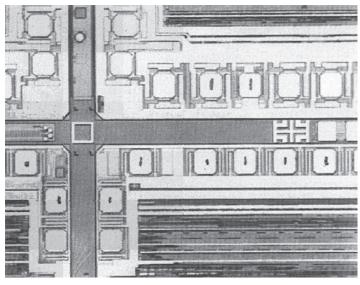

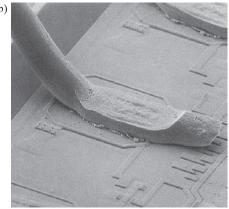

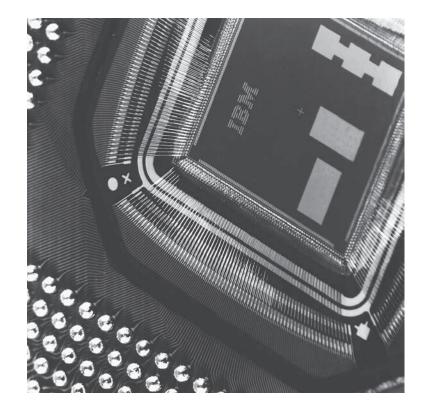

**Multilevel copper metallization of a complementary metal oxide semiconductor (CMOS) chip.** This scanning electron micrograph (scale: 1 cm = 3.5 microns) of a CMOS integrated circuit shows six levels of copper metallization that are used to carry electrical signals on the chip. The inter-metal dielectric insulators have been chemically etched away here to reveal the copper interconnects. (Photograph courtesy of IBM.)

#### SEVENTH EDITION GLOBAL EDITION

# Solid State Electronic Devices

#### BEN G. STREETMAN AND SANJAY KUMAR BANERJEE

Microelectronics Research Center Department of Electrical and Computer Engineering The University of Texas at Austin

Vice President and Editorial Director, ECS: Marcia J.

Horton

Senior Editor: Andrew Gilfillan

Head of Learning Asset Acquisitions, Global Editions:

Laura Dent

Assistant Acquisitions Editor, Global Editions: Aditee

Agarwal

Executive Marketing Manager: Tim Galligan

Marketing Assistant: Jon Bryant

Permissions Project Manager: Karen Sanatar

Senior Managing Editor: Scott Disanno Production Project Manager: Greg Dulles Project Editor, Global Editions: Donald Villamero

Operations Specialist: Linda Sager

Senior Production Manufacturing Controller, Global

Editions: Trudy Kimber

Cover Designer: Lumina Datamatics Ltd.

Cover Image: RaJi/Shutterstock

Media Production Manager, Global Editions: Vikram

Kumar

Pearson Education Limited Edinburgh Gate Harlow Essex CM20 2JE England

and Associated Companies throughout the world

Visit us on the World Wide Web at: www.pearsonglobaleditions.com

© Pearson Education Limited 2016

The rights of Ben G. Streetman and Sanjay Kumar Banerjee to be identified as the authors of this work have been asserted by them in accordance with the Copyright, Designs and Patents Act 1988.

Authorized adaptation from the United States edition, entitled Solid State Electronic Devices, ISBN 978-0-13-335603-8, by Ben G. Streetman and Sanjay Kumar Banerjee, published by Pearson Education © 2015.

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, without either the prior written permission of the publisher or a license permitting restricted copying in the United Kingdom issued by the Copyright Licensing Agency Ltd, Saffron House, 6–10 Kirby Street, London EC1N 8TS.

All trademarks used herein are the property of their respective owners. The use of any trademark in this text does not vest in the author or publisher any trademark ownership rights in such trademarks, nor does the use of such trademarks imply any affiliation with or endorsement of this book by such owners.

British Library Cataloguing-in-Publication Data

A catalogue record for this book is available from the British Library

10987654321

ISBN 10:1-292-06055-7

ISBN 13: 978-1-292-06055-2

Typeset by Jouve India in 10/12 Times Ten LT Std Roman. Printed and bound in Great Britain by Courier Kendallville

## **CONTENTS**

#### PREFACE 13

#### ABOUT THE AUTHORS 17

2.5.2

| 1 |            |                                                                                                                                                                                                                 |

|---|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 |            | TAL PROPERTIES AND GROWTH EMICONDUCTORS 21                                                                                                                                                                      |

|   | 1.1        | Semiconductor Materials 21<br>Crystal Lattices 23<br>1.2.1 Periodic Structures 23<br>1.2.2 Cubic Lattices 25                                                                                                    |

|   | 1.3        | <ul> <li>1.2.3 Planes and Directions 27</li> <li>1.2.4 The Diamond Lattice 29</li> <li>Bulk Crystal Growth 32</li> <li>1.3.1 Starting Materials 32</li> <li>1.3.2 Growth of Single-Crystal Ingots 33</li> </ul> |

|   | 1.4        | <ul><li>1.3.3 Wafers 35</li><li>1.3.4 Doping 36</li><li>Epitaxial Growth 37</li><li>1.4.1 Lattice-Matching in Epitaxial Growth 38</li></ul>                                                                     |

| • | 1.5        | <ul><li>1.4.2 Vapor-Phase Epitaxy 40</li><li>1.4.3 Molecular Beam Epitaxy 42</li><li>Wave Propagation in Discrete, Periodic Structures 44</li></ul>                                                             |

| 2 | ATOM       | AS AND ELECTRONS 52                                                                                                                                                                                             |

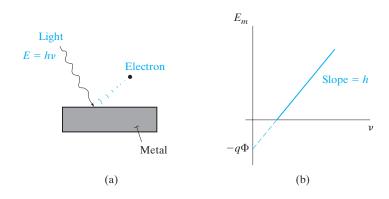

|   | 2.1<br>2.2 | Experimental Observations 54 2.2.1 The Photoelectric Effect 54                                                                                                                                                  |

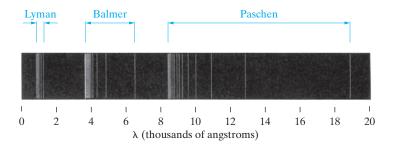

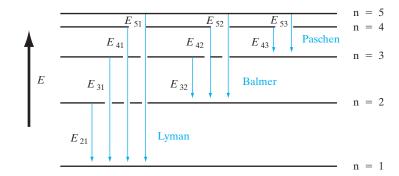

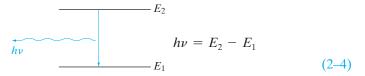

|   | 2.3<br>2.4 | 2.2.2 Atomic Spectra 56 The Bohr Model 57 Quantum Mechanics 61 2.4.1 Probability and the Uncertainty Principle 61 2.4.2 The Schrödinger Wave Equation 63 2.4.3 Potential Well Problem 65                        |

|   | 2.5        | 2.4.4 Tunneling 68 Atomic Structure and the Periodic Table 69 2.5.1 The Hydrogen Atom 70                                                                                                                        |

The Periodic Table 72

| 3 | ENER       | GY BANDS AND CHARGE CARRIERS IN                                                                                                                                                                                                                                                            |

|---|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |            | CONDUCTORS 83                                                                                                                                                                                                                                                                              |

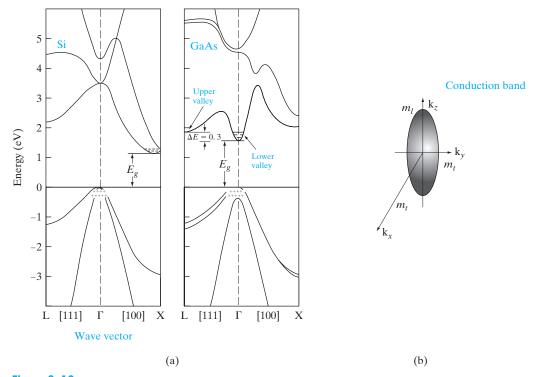

|   | 3.1        | Bonding Forces and Energy Bands in Solids 83 3.1.1 Bonding Forces in Solids 84 3.1.2 Energy Bands 86 3.1.3 Metals, Semiconductors, and Insulators 89 3.1.4 Direct and Indirect Semiconductors 90                                                                                           |

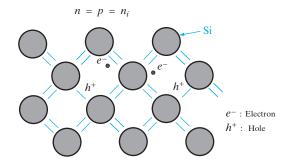

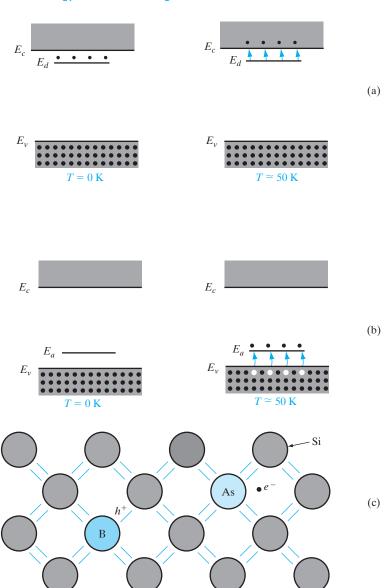

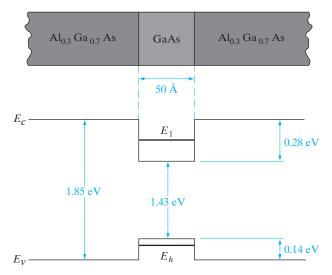

|   | 3.2        | 3.1.5 Variation of Energy Bands with Alloy Composition 92 Charge Carriers in Semiconductors 94 3.2.1 Electrons and Holes 94 3.2.2 Effective Mass 99 3.2.3 Intrinsic Material 103 3.2.4 Extrinsic Material 104                                                                              |

|   | 3.3        | <ul> <li>3.3.1 The Fermi Level 109</li> <li>3.3.2 Electron and Hole Concentrations at Equilibrium 112</li> <li>3.3.3 Temperature Dependence of Carrier Concentrations 117</li> </ul>                                                                                                       |

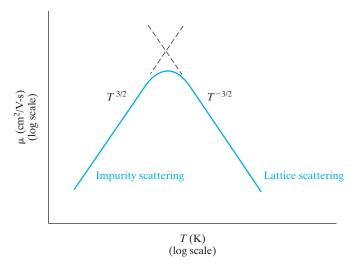

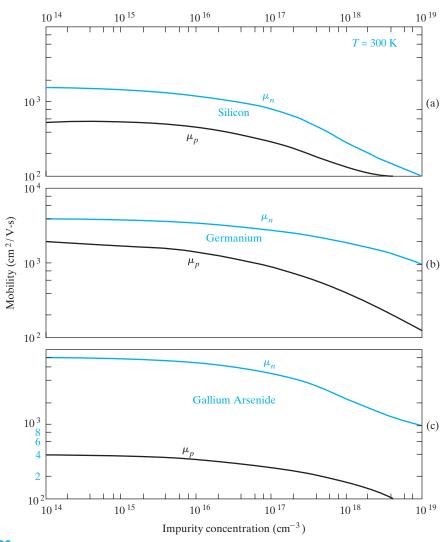

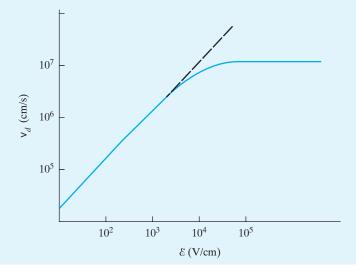

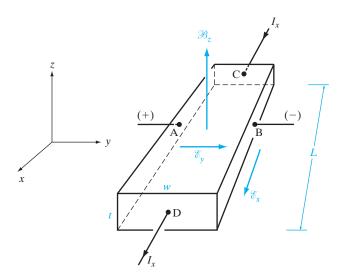

|   | 3.4        | 3.3.4 Compensation and Space Charge Neutrality 119 Drift of Carriers in Electric and Magnetic Fields 120 3.4.1 Conductivity and Mobility 120 3.4.2 Drift and Resistance 125 3.4.3 Effects of Temperature and Doping on Mobility 126 3.4.4 High-Field Effects 129 3.4.5 The Hall Effect 129 |

|   | 3.5        | Invariance of the Fermi Level at Equilibrium 131                                                                                                                                                                                                                                           |

| 4 |            | SS CARRIERS IN SEMICONDUCTORS 142                                                                                                                                                                                                                                                          |

|   | 4.1<br>4.2 | Optical Absorption 142 Luminescence 145 4.2.1 Photoluminescence 146 4.2.2 Electroluminescence 148                                                                                                                                                                                          |

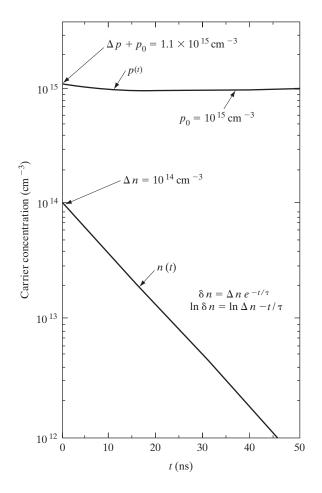

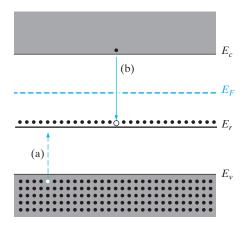

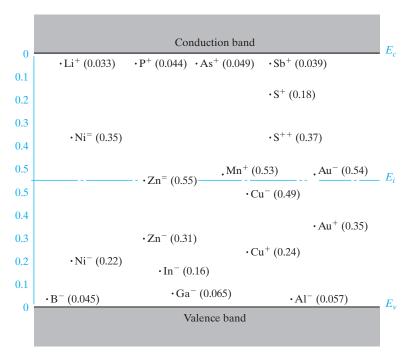

|   | 4.3        | Carrier Lifetime and Photoconductivity 148 4.3.1 Direct Recombination of Electrons and Holes 149 4.3.2 Indirect Recombination; Trapping 151 4.3.3 Steady State Carrier Generation; Quasi-Fermi Levels 154 4.3.4 Photoconductive Devices 156                                                |

|   | 4.4        | Diffusion of Carriers 157 4.4.1 Diffusion Processes 158 4.4.2 Diffusion and Drift of Carriers; Built-in Fields 160 4.4.3 Diffusion and Recombination; The Continuity Equation 163                                                                                                          |

Contents 7

Steady State Carrier Injection; Diffusion Length 165

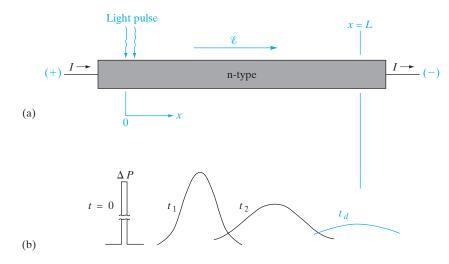

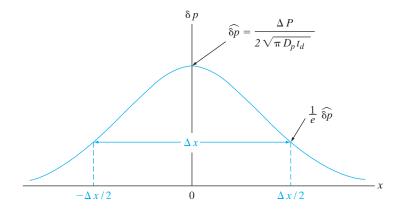

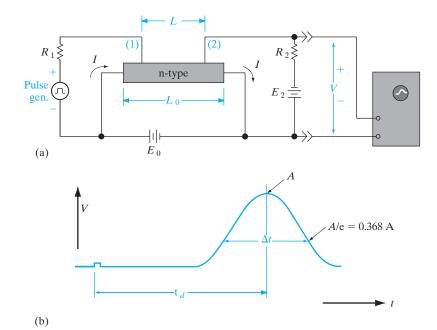

The Haynes–Shockley Experiment 167

4.4.4

4.4.5

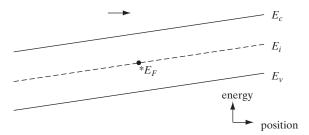

|            | 4.4.6          | Gradients in the Quasi-Fermi Levels 1/0                   |

|------------|----------------|-----------------------------------------------------------|

| JUNC       | TIONS          | 179                                                       |

| 5.1        | Fabrica        | ation of p-n Junctions 179                                |

|            |                | Thermal Oxidation 180                                     |

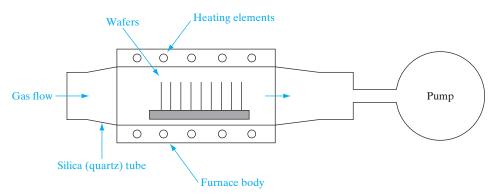

|            |                | Diffusion 181                                             |

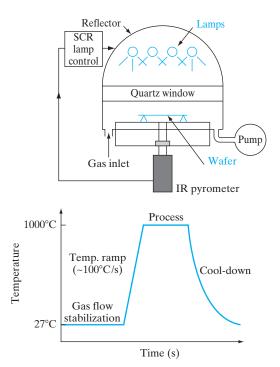

|            |                | Rapid Thermal Processing 183                              |

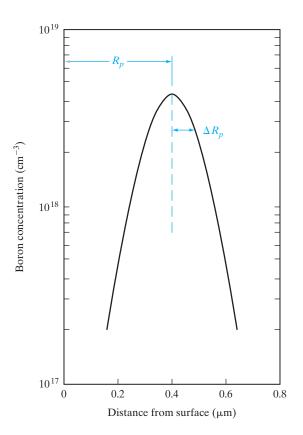

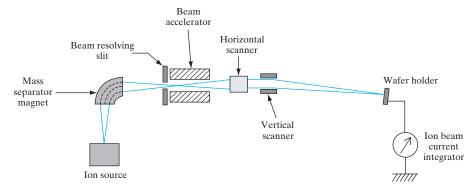

|            |                | lon Implantation 184                                      |

|            | 5.1.5          | Chemical Vapor Deposition (CVD) 187                       |

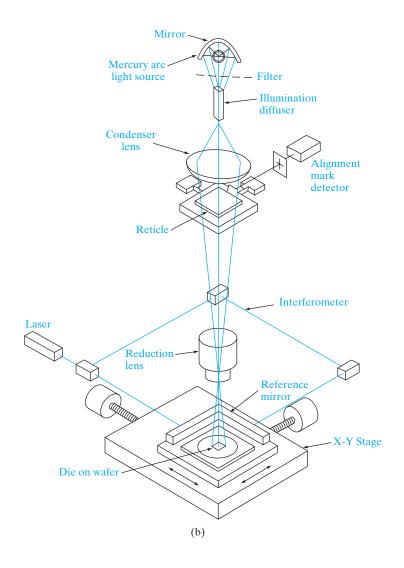

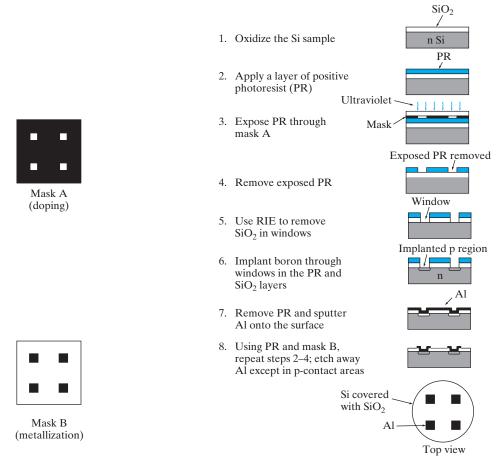

|            |                | Photolithography 188                                      |

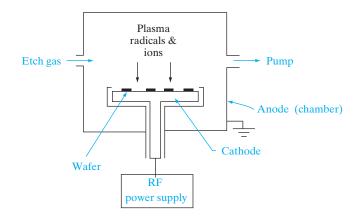

|            |                | Etching 191                                               |

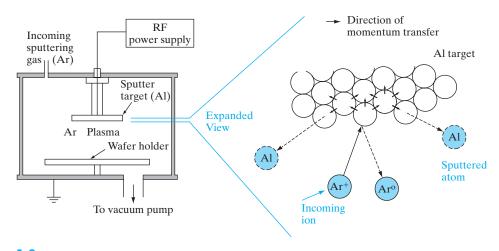

|            |                | Metallization 193                                         |

| 5.2        |                | rium Conditions 194                                       |

|            |                | The Contact Potential 195                                 |

|            |                | Equilibrium Fermi Levels 200                              |

| <i>F</i> 2 |                | Space Charge at a Junction 200                            |

| 5.3        |                | rd- and Reverse-Biased                                    |

|            |                | ns; Steady State Conditions 205                           |

|            |                | Qualitative Description of Current Flow at a Junction 205 |

|            |                | Carrier Injection 209 Reverse Bias 218                    |

| 5.4        |                | e-Bias Breakdown 220                                      |

| 5.4        |                | Zener Breakdown 221                                       |

|            |                | Avalanche Breakdown 222                                   |

|            |                | Rectifiers 225                                            |

|            |                | The Breakdown Diode 228                                   |

| 5.5        | Transie        | ent and A-C Conditions 229                                |

|            | 5.5.1          | Time Variation of Stored Charge 229                       |

|            | 5.5.2          | Reverse Recovery Transient 232                            |

|            |                | Switching Diodes 236                                      |

|            |                | Capacitance of p-n Junctions 236                          |

| - ,        |                | The Varactor Diode 241                                    |

| 5.6        |                | ons from the Simple Theory 242                            |

|            |                | Effects of Contact Potential on Carrier Injection 243     |

|            |                | Recombination and Generation in the Transition Region 245 |

|            |                | Ohmic Losses 247                                          |

| 5.7        |                | Graded Junctions 248                                      |

| J./        |                | Semiconductor Junctions 251                               |

|            | 5.7.1<br>5.7.2 | ,                                                         |

|            | J./ .Z         | Rectifying Contacts 253                                   |

|   |        | 5.7.3 Ohmic Contacts 255 5.7.4 Typical Schottky Barriers 257                                  |

|---|--------|-----------------------------------------------------------------------------------------------|

|   | 5.8    |                                                                                               |

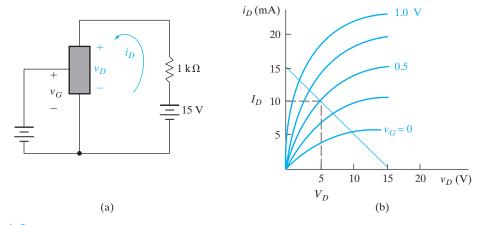

| 6 | FIELD- | EFFECT TRANSISTORS 277                                                                        |

|   | 6.1    | Transistor Operation 278                                                                      |

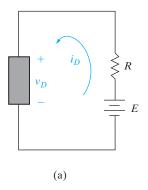

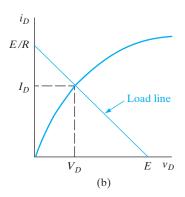

|   |        | 6.1.1 The Load Line 278                                                                       |

|   | / 0    | 6.1.2 Amplification and Switching 279                                                         |

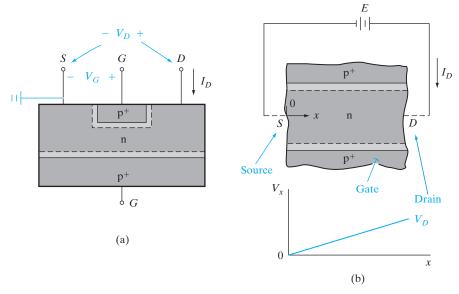

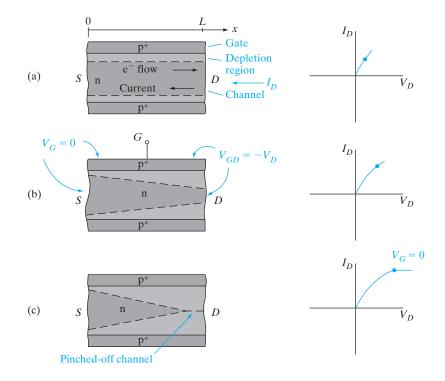

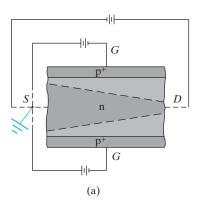

|   | 0.2    | The Junction FET 280                                                                          |

|   |        | 6.2.1 Pinch-off and Saturation 281 6.2.2 Gate Control 283                                     |

|   |        |                                                                                               |

|   | 63     | 6.2.3 Current–Voltage Characteristics 285 The Metal–Semiconductor FET 287                     |

|   | 0.5    | 6.3.1 The GaAs MESFET 287                                                                     |

|   |        | 6.3.2 The High Electron Mobility Transistor (HEMT) 288                                        |

|   |        | 6.3.3 Short Channel Effects 290                                                               |

|   | 6.4    | The Metal-Insulator-Semiconductor FET 291                                                     |

|   |        | 6.4.1 Basic Operation and Fabrication 291                                                     |

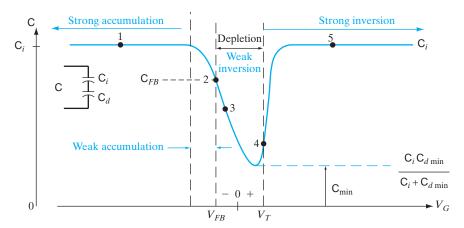

|   |        | 6.4.2 The Ideal MOS Capacitor 295                                                             |

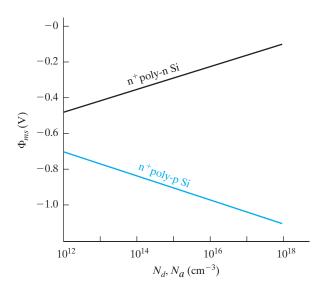

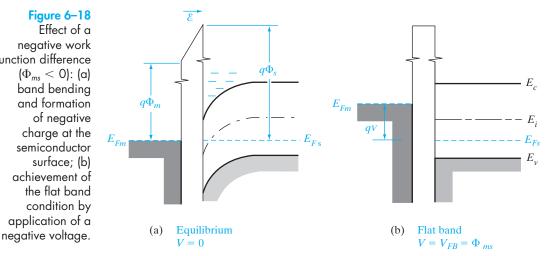

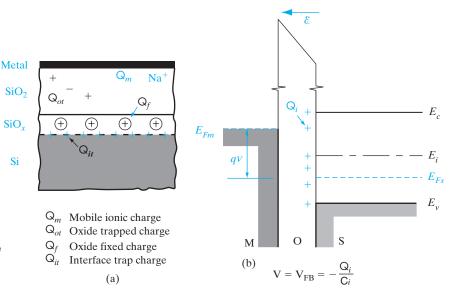

|   |        | 6.4.3 Effects of Real Surfaces 306                                                            |

|   |        | 6.4.4 Threshold Voltage 309                                                                   |

|   |        | 6.4.5 MOS Capacitance–Voltage Analysis 311                                                    |

|   |        | 6.4.6 Time-Dependent Capacitance Measurements 315                                             |

|   |        | 6.4.7 Current-Voltage Characteristics of MOS Gate Oxides 316                                  |

|   | 6.5    | The MOS Field-Effect Transistor 319                                                           |

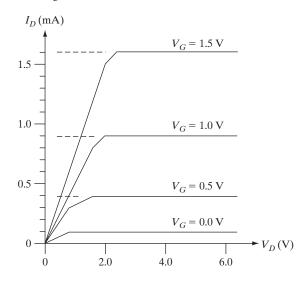

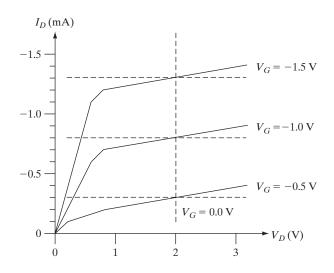

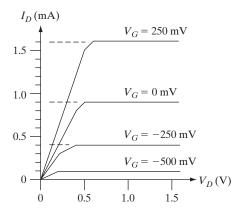

|   |        | 6.5.1 Output Characteristics 319                                                              |

|   |        | 6.5.2 Transfer Characteristics 322                                                            |

|   |        | 6.5.3 Mobility Models 325                                                                     |

|   |        | 6.5.4 Short Channel MOSFET I–V Characteristics 327                                            |

|   |        | 6.5.5 Control of Threshold Voltage 329                                                        |

|   |        | 6.5.6 Substrate Bias Effects—the "body" effect 332                                            |

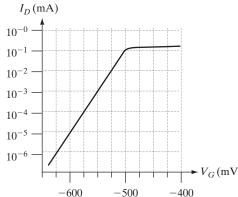

|   |        | 6.5.7 Subthreshold Characteristics 336                                                        |

|   |        | 6.5.8 Equivalent Circuit for the MOSFET 338 6.5.9 MOSFET Scaling and Hot Electron Effects 341 |

|   |        | 6.5.9 MOSFET Scaling and Hot Electron Effects 341 6.5.10 Drain-Induced Barrier Lowering 345   |

|   |        | 6.5.11 Short Channel Effect and Narrow Width Effect 347                                       |

|   |        | 6.5.12 Gate-Induced Drain Leakage 349                                                         |

|   | 6.6    |                                                                                               |

|   | 0.0    | 6.6.1 Metal Gate-High-k 350                                                                   |

|   |        | 6.6.2 Enhanced Channel Mobility Materials and Strained Si FETs 351                            |

|   |        | 6.6.3 SOI MOSFETs and FinFETs 353                                                             |

Contents 9

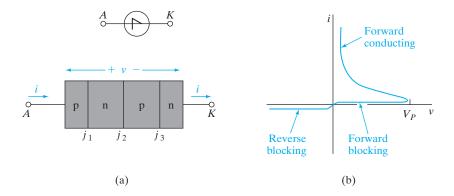

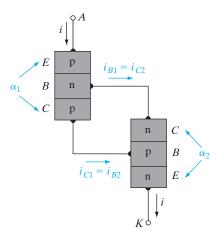

| 7 | BIPOL      | AR JUNCTION TRANSISTORS 368                                                                                                                                                                                                                 |          |

|---|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|   | 7.1<br>7.2 |                                                                                                                                                                                                                                             |          |

|   |            | Minority Carrier Distributions and Terminal Currents 3                                                                                                                                                                                      | 78<br>79 |

|   | 7.5        | 7.4.4 Current transfer Katio 380 Generalized Biasing 387 7.5.1 The Coupled-Diode Model 388 7.5.2 Charge Control Analysis 393                                                                                                                |          |

|   | 7.6        | Switching 395                                                                                                                                                                                                                               |          |

|   |            | <ul><li>7.6.1 Cutoff 396</li><li>7.6.2 Saturation 397</li><li>7.6.3 The Switching Cycle 398</li><li>7.6.4 Specifications for Switching Transistors 399</li></ul>                                                                            |          |

|   | 7.7        | Other Important Effects 400 7.7.1 Drift in the Base Region 401 7.7.2 Base Narrowing 402 7.7.3 Avalanche Breakdown 403 7.7.4 Injection Level; Thermal Effects 405 7.7.5 Base Resistance and Emitter Crowding 406 7.7.6 Gummel–Poon Model 408 |          |

|   | 7.8        | 7.7.7 Kirk Effect 411 Frequency Limitations of Transistors 414 7.8.1 Capacitance and Charging Times 414 7.8.2 Transit Time Effects 417 7.8.3 Webster Effect 418 7.8.4 High-Frequency Transistors 418                                        |          |

|   | 7.9        | Heterojunction Bipolar Transistors 420                                                                                                                                                                                                      |          |

| Q | 0.770      |                                                                                                                                                                                                                                             |          |

| 0 | OPTO       | DELECTRONIC DEVICES 430                                                                                                                                                                                                                     |          |

|   | 8.1        | Photodiodes 430 8.1.1 Current and Voltage in an Illuminated Junction 431 8.1.2 Solar Cells 434 8.1.3 Photodetectors 437 8.1.4 Gain, Bandwidth, and Signal-to-Noise Ratio                                                                    |          |

of Photodetectors 439

|              | 8.2   | Light-Emitting Diodes 442                             |

|--------------|-------|-------------------------------------------------------|

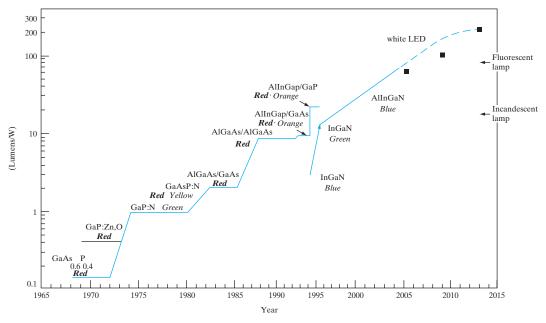

|              |       | 8.2.1 Light-Emitting Materials 443                    |

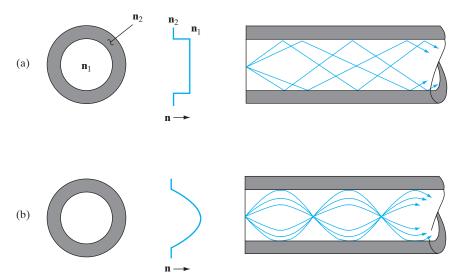

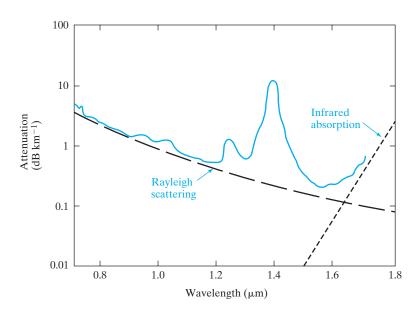

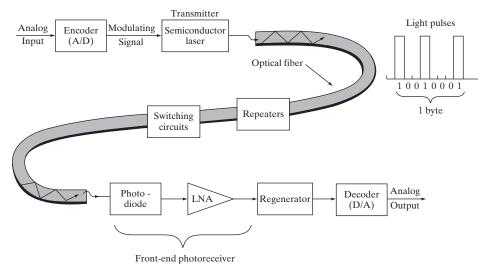

|              |       | 8.2.2 Fiber-Optic Communications 447                  |

|              | 8.3   | Lasers 450                                            |

|              | 8.4   | Semiconductor Lasers 454                              |

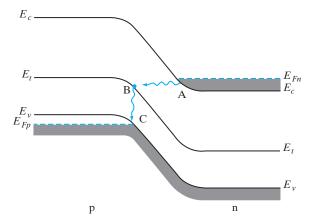

|              |       | 8.4.1 Population Inversion at a Junction 455          |

|              |       | 8.4.2 Emission Spectra for p-n Junction Lasers 457    |

|              |       | 8.4.3 The Basic Semiconductor Laser 458               |

|              |       | 8.4.4 Heterojunction Lasers 459                       |

|              |       | 8.4.5 Materials for Semiconductor Lasers 462          |

|              |       | 8.4.6 Quantum Cascade Lasers 464                      |

| )            |       |                                                       |

|              | INTEC | GRATED CIRCUITS 472                                   |

|              | 9.1   | Background 473                                        |

|              |       | 9.1.1 Advantages of Integration 473                   |

|              |       | 9.1.2 Types of Integrated Circuits 475                |

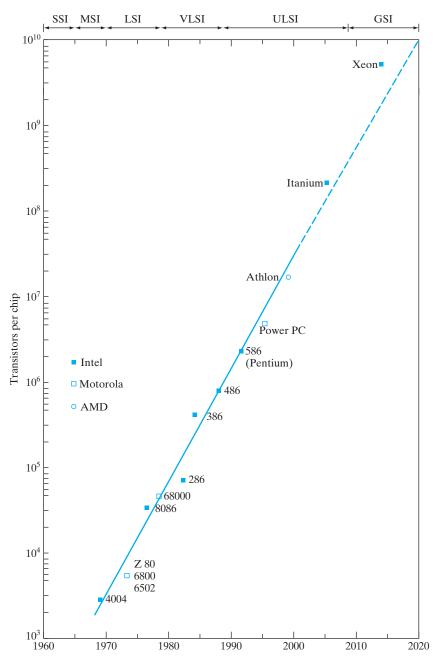

|              | 9.2   | Evolution of Integrated Circuits 476                  |

|              | 9.3   | Monolithic Device Elements 479                        |

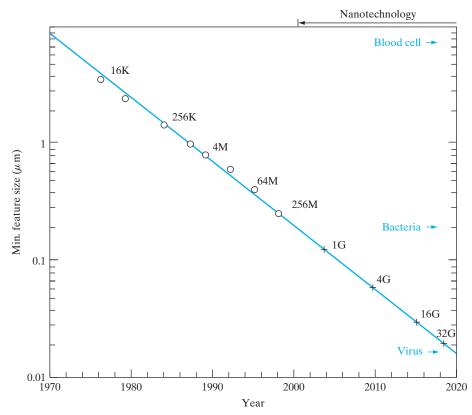

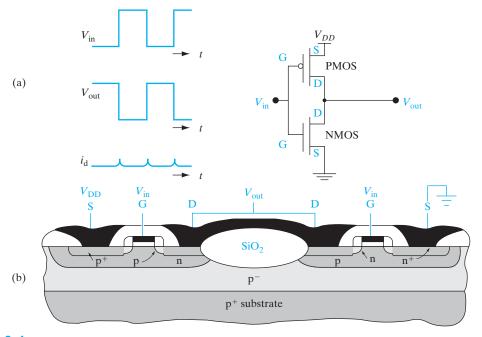

|              |       | 9.3.1 CMOS Process Integration 479                    |

|              | 0 1   | 9.3.2 Integration of Other Circuit Elements 494       |

|              | 9.4   | Charge Transfer Devices 500                           |

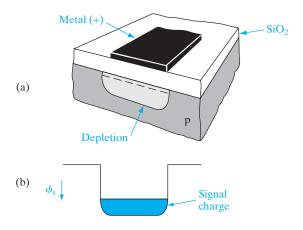

|              |       | 9.4.1 Dynamic Effects in MOS Capacitors 501           |

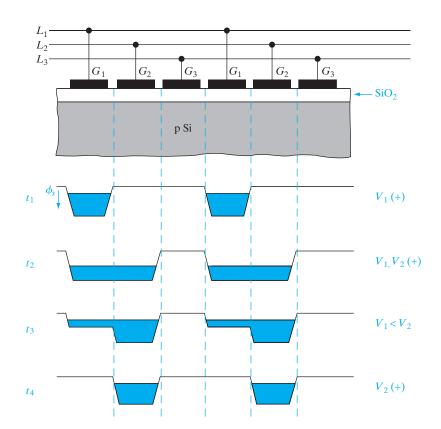

|              |       | 9.4.2 The Basic CCD 502                               |

|              |       | 9.4.3 Improvements on the Basic Structure 503         |

|              | 0.5   | 9.4.4 Applications of CCDs 504                        |

|              | 9.5   | Ultra Large-Scale Integration (ULSI) 505              |

|              |       | 9.5.1 Logic Devices 507                               |

|              | 0.4   | 9.5.2 Semiconductor Memories 517                      |

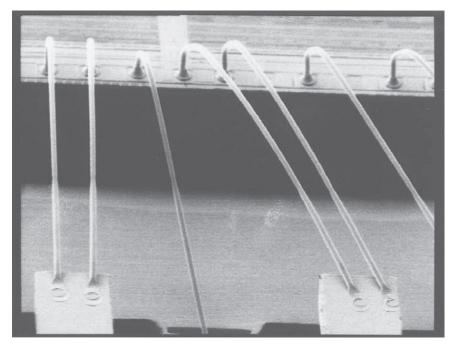

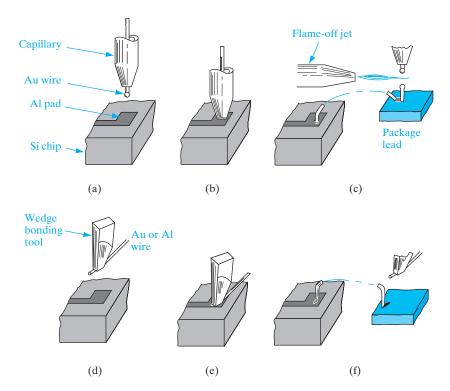

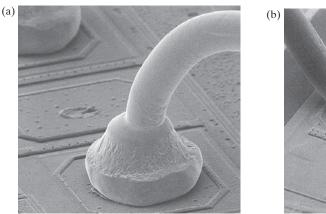

|              | 9.0   | Testing, Bonding, and Packaging 530 9.6.1 Testing 531 |

|              |       | 9.6.2 Wire Bonding 531                                |

|              |       | 9.6.3 Flip-Chip Techniques 535                        |

|              |       | 9.6.4 Packaging 535                                   |

|              |       | 7.0.4 Tackaging 555                                   |

| $\mathbf{O}$ | HIGH. | FREQUENCY, HIGH-POWER AND                             |

|              |       | OELECTRONIC DEVICES 541                               |

|              |       | Tunnel Diodes 541                                     |

|              | 10.1  | 10.1.1 Degenerate Semiconductors 541                  |

|              | 10.2  | The IMPATT Diode 545                                  |

|              |       | The Gunn Diode 548                                    |

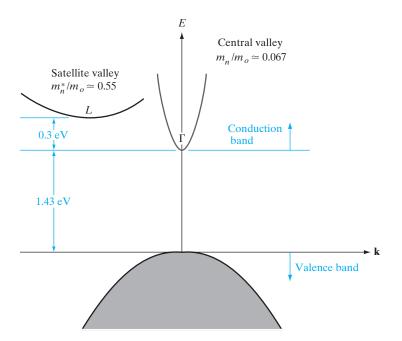

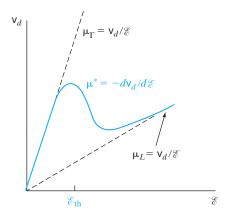

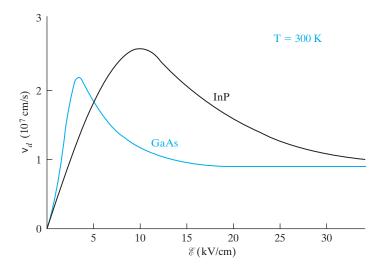

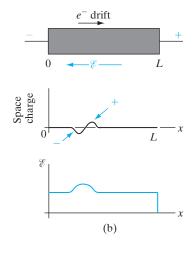

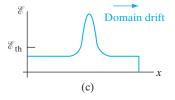

10.3.1 The Transferred-Electron Mechanism 548

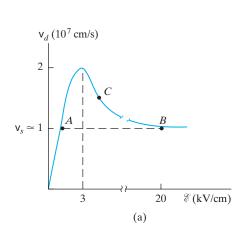

10.3.2 Formation and Drift of Space Charge Domains 551

Contents 11

#### **APPENDICES**

I. Definitions of Commonly Used Symbols 575

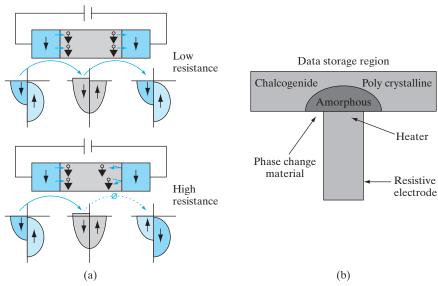

10.7.5 Nanoelectronic Resistive Memory 570

- II. Physical Constants and Conversion Factors 579

- III. Properties of Semiconductor Materials 580

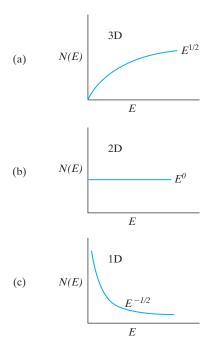

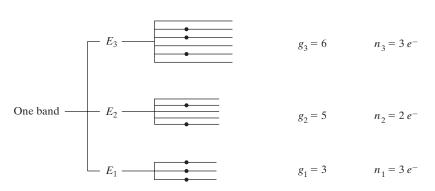

- IV. Derivation of the Density of States in the Conduction Band 581

- V. Derivation of Fermi-Dirac Statistics 586

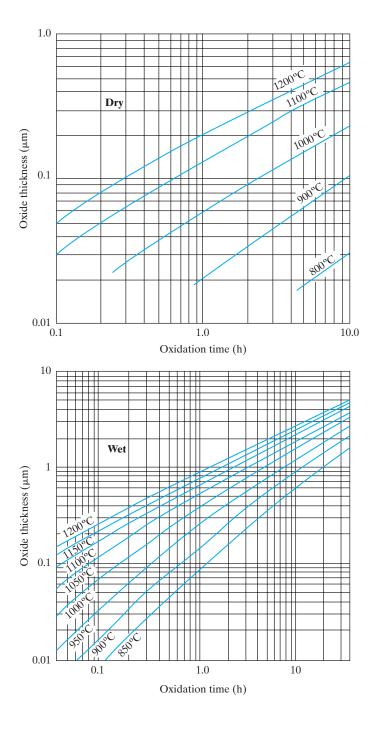

- VI. Dry and Wet Thermal Oxide Thickness Grown on Si (100) as a Function of Time and Temperature 589

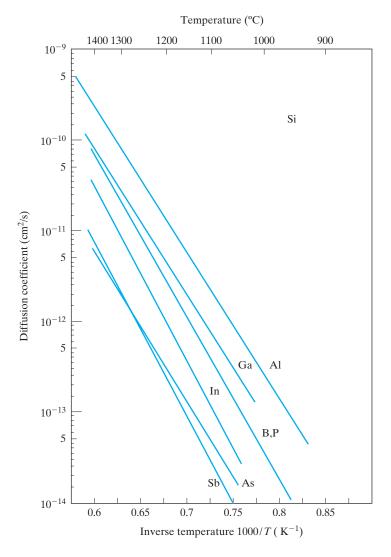

- VII. Solid Solubilities of Impurities in Si 591

- VIII. Diffusivities of Dopants in Si and SiO<sub>2</sub> 592

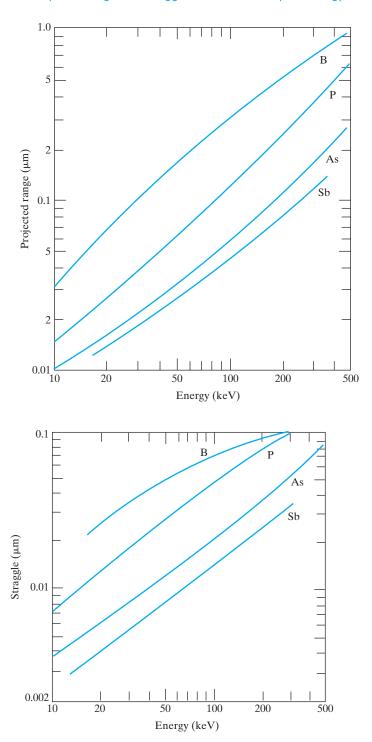

- IX. Projected Range and Straggle as Function of Implant Energy in Si 594

ANSWERS TO SELECTED SELF QUIZ QUESTIONS 596

INDEX 600

This book is an introduction to semiconductor devices for undergraduate electrical engineers, other interested students, and practicing engineers and scientists whose understanding of modern electronics needs updating. The book is organized to bring students with a background in sophomore physics to a level of understanding that will allow them to read much of the current literature on new devices and applications.

An undergraduate course in electronic devices has two basic purposes: (1) to provide students with a sound understanding of existing devices, so that their studies of electronic circuits and systems will be meaningful and (2) to develop the basic tools with which they can later learn about newly developed devices and applications. Perhaps the second of these objectives is the more important in the long run; it is clear that engineers and scientists who deal with electronics will continually be called upon to learn about new devices and processes in the future. For this reason, we have tried to incorporate the basics of semiconductor materials and conduction processes in solids, which arise repeatedly in the literature when new devices are explained. Some of these concepts are often omitted in introductory courses, with the view that they are unnecessary for understanding the fundamentals of junctions and transistors. We believe this view neglects the important goal of equipping students for the task of understanding a new device by reading the current literature. Therefore, in this text most of the commonly used semiconductor terms and concepts are introduced and related to a broad range of devices.

**GOALS**

- updated discussion of MOS devices, both in the underlying theory of ballistic FETs as well as discussion of advanced MOSFETs such as FinFETs, strained Si devices, metal gate/ high-k devices, III-V high channel mobility devices

- updated treatment of optoelectronic devices, including high bandgap nitride semiconductors and quantum cascade lasers

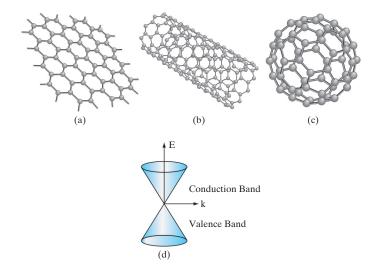

- brand new section on nanoelectronics to introduce students to exciting concepts such as 2D materials including graphene and topological insulators, 1D nanowires and nanotubes, and 0D quantum dots;

- discussion of spintronics, and novel resistive and phase change memories

- about 100 new problems, and current references which extend concepts in the text.

WHAT IS NEW IN THIS EDITION

#### **READING LISTS**

As a further aid in developing techniques for independent study, the reading list at the end of each chapter includes a few articles which students can read comfortably as they study this book. We do not expect that students will read all articles recommended in the reading lists; nevertheless, some exposure to periodicals is useful in laying the foundation for a career of constant updating and self-education. We have also added a summary of the key concepts at the end of each chapter.

#### **PROBLEMS**

One of the keys to success in understanding this material is to work problems that exercise the concepts. The problems at the end of each chapter are designed to facilitate learning the material. Very few are simple "plug-in" problems. Instead, they are chosen to reinforce or extend the material presented in the chapter. In addition, we have added "self quiz" problems that test the conceptual understanding on the part of the students.

#### **UNITS**

In keeping with the goals described above, examples and problems are stated in terms of units commonly used in the semiconductor literature. The basic system of units is rationalized MKS, although cm is often used as a convenient unit of length. Similarly, electron volts (eV) are often used rather than joules (J) to measure the energy of electrons. Units for various quantities are given in Appendices I and II.

#### **PRESENTATION**

In presenting this material at the undergraduate level, one must anticipate a few instances which call for a phrase such as "It can be shown . . ." This is always disappointing; on the other hand, the alternative is to delay study of solid state devices until the graduate level, where statistical mechanics, quantum theory, and other advanced background can be freely invoked. Such a delay would result in a more elegant treatment of certain subjects, but it would prevent undergraduate students from enjoying the study of some very exciting devices.

The discussion includes both silicon and compound semiconductors, to reflect the continuing growth in importance for compounds in optoelectronic and high-speed device applications. Topics such as heterojunctions, lattice-matching using ternary and quaternary alloys, variation of band gap with alloy composition, and properties of quantum wells add to the breadth of the discussion. Not to be outdone by the compounds, silicon-based devices have continued their dramatic record of advancement. The discussion of FET structures and Si integrated circuits reflects these advancements. Our objective is not to cover all the latest devices, which can only be done in the journal and conference literature. Instead, we have chosen devices to discuss which are broadly illustrative of important principles.

**Preface** 15

The first four chapters of the book provide background on the nature of semiconductors and conduction processes in solids (Chapters 3, 4). Included is a brief introduction to quantum concepts (Chapter 2) for those students who do not already have this background from other courses. Chapter 5 describes the p-n junction and some of its applications. Chapters 6 and 7 deal with the principles of transistor operation. Chapter 8 covers optoelectronics, and Chapter 9 discusses integrated circuits. Chapter 10 applies the theory of junctions and conduction processes to microwave and power devices. A completely new section on nanoelectronics has been added. All of the devices covered are important in today's electronics; furthermore, learning about these devices should be an enjoyable and rewarding experience. We hope this book provides that kind of experience for its readers.

The seventh edition benefits greatly from comments and suggestions provided by students and teachers of the first six editions. The book's readers have generously provided comments which have been invaluable in developing the present version. We remain indebted to those persons mentioned in the Preface of the first six editions, who contributed so much to the development of the book. In particular, Nick Holonyak has been a source of continuing information and inspiration for all seven editions. Additional thanks go to our colleagues at UT-Austin who have provided special assistance, particularly Leonard Frank Register, Emanuel Tutuc, Ray Chen, Ananth Dodabalapur, Seth Bank, Misha Belkin, Zheng Wang, Neal Hall, Deji Akinwande, Jack Lee, and Dean Neikirk. Hema Movva provided useful assistance with the typing of the homework solutions. We thank the many companies and organizations cited in the figure captions for generously providing photographs and illustrations of devices and fabrication processes. Bob Doering at TI, Mark Bohr at Intel, Chandra Mouli at Micron, Babu Chalamala at MEMC and Kevin Lally at TEL deserve special mention for the new pictures in this edition. Finally, we recall with gratitude many years of association with Joe Campbell, Karl Hess, and the late Al Tasch, valued colleagues and friends.

Ben G. Streetman Sanjay Kumar Banerjee

The publishers would like to thank the following for their contribution to the Global Edition:

#### Contributor:

Rikmantra Basu, Assistant Professor, Electronics and Communication Engineering (ECE) Department, National Institute of Technology (NIT) Delhi

#### Reviewers:

Sunanda Khosla (writer) Prof. Tan Chuan Seng, Nanyang Technological University Prof. Dr. habil. Jörg Schulze, University of Stuttgart

**ACKNOW-LEDGMENTS**

### PRENTICE HALL SERIES IN SOLID STATE PHYSICAL ELECTRONICS

Nick Holonyak Jr., Editor

Cheo FIBER OPTICS: DEVICES AND SYSTEMS SECOND EDITION

Haus WAVES AND FIELDS IN OPTOELECTRONICS

Kroemer QUANTUM MECHANICS FOR ENGINEERING, MATERIALS SCIENCE,

AND APPLIED PHYSICS

Nussbaum CONTEMPORARY OPTICS FOR SCIENTISTS AND ENGINEERS

Peyghambarian/Koch/Mysyrowicz INTRODUCTION TO SEMICONDUCTOR OPTICS

Shur PHYSICS OF SEMICONDUCTOR DEVICES

SocIof DESIGN AND APPLICATIONS OF ANALOG INTEGRATED CIRCUITS

Streetman/Banerjee SOLID STATE ELECTRONIC DEVICES SEVENTH EDITION

Verdeyen LASER ELECTRONICS THIRD EDITION

Wolfe/Holonyak/Stillman PHYSICAL PROPERTIES OF SEMICONDUCTORS

#### **ABOUT THE AUTHORS**

Ben G. Streetman is Dean Emeritus of the Cockrell School of Engineering at The University of Texas at Austin. He is an Emeritus Professor of Electrical and Computer Engineering, where he held the Dula D. Cockrell Centennial Chair. He was the founding Director of the Microelectronics Research Center (1984–1996) and served as Dean of Engineering from 1996 to 2008. His teaching and research interests involve semiconductor materials and devices. After receiving a Ph.D. from The University of Texas at Austin (1966) he was on the faculty (1966–1982) of the University of Illinois at Urbana-Champaign. He returned to The University of Texas at Austin in 1982. His honors include the Education Medal of the Institute of Electrical and Electronics Engineers (IEEE), the Frederick Emmons Terman Medal of the American Society for Engineering Education (ASEE), and the Heinrich Welker Medal from the International Conference on Compound Semiconductors. He is a member of the National Academy of Engineering and the American Academy of Arts and Sciences. He is a Fellow of the IEEE and the Electrochemical Society. He has been honored as a Distinguished Alumnus of The University of Texas at Austin and as a Distinguished Graduate of the UT College of Engineering. He has received the General Dynamics Award for Excellence in Engineering Teaching, and was honored by the Parents' Association as a Teaching Fellow for outstanding teaching of undergraduates. He has served on numerous panels and committees in industry and government, and several corporate boards. He has published more than 290 articles in the technical literature. Thirtyfour students of Electrical Engineering, Materials Science, and Physics have received their Ph.D.s under his direction.

Sanjay Kumar Banerjee is the Cockrell Chair Professor of Electrical and Computer Engineering, and Director of the Microelectronics Research Center at The University of Texas at Austin. He received his B.Tech. from the Indian Institute of Technology, Kharagpur, and his M.S. and Ph.D. from the University of Illinois at Urbana-Champaign in 1979, 1981, and 1983, respectively, in electrical engineering. He worked at TI from 1983–1987 on the world's first 4Megabit DRAM, for which he was a co-recipient of an ISSCC Best Paper Award. He has more than 900 archival refereed publications and conference papers, 30 U.S. patents, and has supervised over 50 Ph.D. students. His honors include the NSF Presidential Young Investigator Award (1988), the Texas Atomic Energy Centennial Fellowship (1990–1997), Cullen Professorship (1997–2001), and the Hocott Research Award from the University of Texas. He has received the ECS Callinan Award (2003), Industrial R&D 100 Award (2004), Distinguished Alumnus Award, IIT (2005), IEEE Millennium Medal (2000) and IEEE Andrew S. Grove Award (2014). He is a Fellow of IEEE, APS and AAAS. He is interested in beyond-CMOS nanoelectronic transistors based on 2D materials and spintronics, fabrication and modeling of advanced MOSFETs, and solar cells.

### **Solid State Electronic Devices**

#### Chapter 1

# Crystal Properties and Growth of Semiconductors

#### **OBJECTIVES**

- 1. Describe what a semiconductor is

- 2. Perform simple calculations about crystals

- 3. Understand what is involved in bulk Czochralski and thin-film epitaxial crystal growth

- 4. Learn about crystal defects

In studying solid state electronic devices we are interested primarily in the electrical behavior of solids. However, we shall see in later chapters that the transport of charge through a metal or a semiconductor depends not only on the properties of the electron but also on the arrangement of atoms in the solid. In this chapter we shall discuss some of the physical properties of semiconductors compared with other solids, the atomic arrangements of various materials, and some methods of growing semiconductor crystals. Topics such as crystal structure and crystal growth technology are often the subjects of books rather than introductory chapters; thus we shall consider only a few of the more important and fundamental ideas that form the basis for understanding electronic properties of semiconductors and device fabrication.

Semiconductors are a group of materials having electrical conductivities intermediate between metals and insulators. It is significant that the conductivity of these materials can be varied over orders of magnitude by changes in temperature, optical excitation, and impurity content. This variability of electrical properties makes the semiconductor materials natural choices for electronic device investigations.

Semiconductor materials are found in column IV and neighboring columns of the periodic table (Table 1–1). The column IV semiconductors, silicon and germanium, are called *elemental* semiconductors because they are composed of single species of atoms. In addition to the elemental materials, compounds of column III and column V atoms, as well as certain combinations from II and VI, and from IV, make up the *compound* semiconductors.

1.1 SEMICONDUCTOR MATERIALS As Table 1–1 indicates, there are numerous semiconductor materials. As we shall see, the wide variety of electronic and optical properties of these semiconductors provides the device engineer with great flexibility in the design of electronic and optoelectronic functions. The elemental semiconductor Ge was widely used in the early days of semiconductor development for transistors and diodes. Silicon is now used for the majority of rectifiers, transistors, and integrated circuits (ICs). However, the compounds are widely used in high-speed devices and devices requiring the emission or absorption of light. The two-element (*binary*) III–V compounds such as GaN, GaP, and GaAs are common in light-emitting diodes (LEDs). As discussed in Section 1.2.4, three-element (*ternary*) compounds such as GaAsP and four-element (*quaternary*) compounds such as InGaAsP can be grown to provide added flexibility in choosing materials properties.

Fluorescent materials such as those used in television screens usually are II–VI compound semiconductors such as ZnS. Light detectors are commonly made with InSb, CdSe, or other compounds such as PbTe and HgCdTe. Si and Ge are also widely used as infrared and nuclear radiation detectors. Light-emitting diodes are made using GaN and other III–V compounds. Semiconductor lasers are made using GaAs, AlGaAs, and other ternary and quaternary compounds.

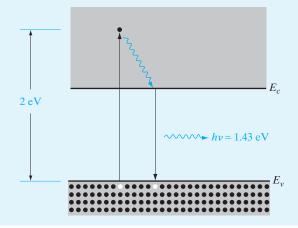

One of the most important characteristics of a semiconductor, which distinguishes it from metals and insulators, is its *energy band gap*. This property, which we will discuss in detail in Chapter 3, determines among other things the wavelengths of light that can be absorbed or emitted by the semiconductor. For example, the band gap of GaAs is about 1.43 electron volts (eV), which

| Table 1-1 | Common semiconductor materials: (a) the portion of the periodic table where |  |

|-----------|-----------------------------------------------------------------------------|--|

| semicondu | ors occur; (b) elemental and compound semiconductors.                       |  |

| (a) | II        | III          | IV           | V            | VI |

|-----|-----------|--------------|--------------|--------------|----|

|     |           | В            | С            | Ν            |    |

|     |           | Al           | Si           | Р            | S  |

|     | Zn        | Ga           | Ge           | As           | Se |

|     | Cd        | ln           |              | Sb           | Те |

|     |           |              | Binary III–V | Binary II–VI |    |

| (b) | Elemental | IV compounds | compounds    | compounds    |    |

|     | Si        | SiC          | AlP          | ZnS          |    |

|     | Ge        | SiGe         | AlAs         | ZnSe         |    |

|     |           |              | AlSb         | ZnTe         |    |

|     |           |              | GaN          | CdS          |    |

|     |           |              | GaP          | CdSe         |    |

|     |           |              | GaAs         | CdTe         |    |

|     |           |              | GaSb         |              |    |

|     |           |              | InP          |              |    |

|     |           |              | InAs         |              |    |

|     |           |              | InSb         |              |    |

corresponds to light wavelengths in the near infrared. In contrast, GaP has a band gap of about 2.3 eV, corresponding to wavelengths in the green portion of the spectrum. The band gap  $E_{\rm g}$  for various semiconductor materials is listed along with other properties in Appendix III. As a result of the wide variety of semiconductor band gaps, LEDs and lasers can be constructed with wavelengths over a broad range of the infrared and visible portions of the spectrum.

The electronic and optical properties of semiconductor materials are strongly affected by impurities, which may be added in precisely controlled amounts. Such impurities are used to vary the conductivities of semiconductors over wide ranges and even to alter the nature of the conduction processes from conduction by negative charge carriers to positive charge carriers. For example, an impurity concentration of one part per million can change a sample of Si from a poor conductor to a good conductor of electric current. This process of controlled addition of impurities, called *doping*, will be discussed in detail in subsequent chapters.

To investigate these useful properties of semiconductors, it is necessary to understand the atomic arrangements in the materials. Obviously, if slight alterations in purity of the original material can produce such dramatic changes in electrical properties, then the nature and specific arrangement of atoms in each semiconductor must be of critical importance. Therefore, we begin our study of semiconductors with a brief introduction to crystal structure.

In this section we discuss the arrangements of atoms in various solids. We shall distinguish between single crystals and other forms of materials and then investigate the periodicity of crystal lattices. Certain important crystallographic terms will be defined and illustrated in reference to crystals having a basic cubic structure. These definitions will allow us to refer to certain planes and directions within a lattice. Finally, we shall investigate the diamond lattice; this structure, with some variations, is typical of most of the semiconductor materials used in electronic devices.

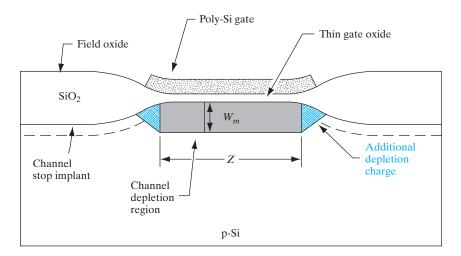

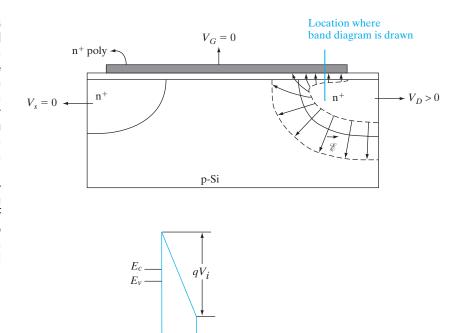

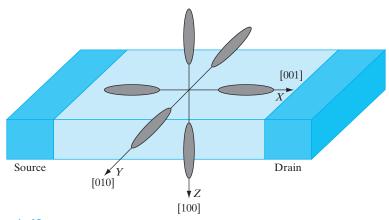

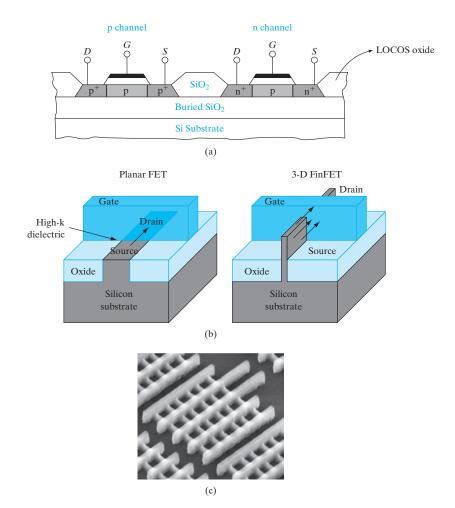

#### 1.2.1 Periodic Structures

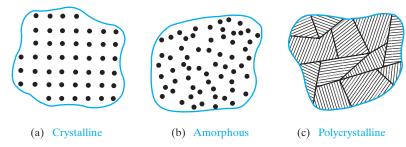

A crystalline solid is distinguished by the fact that the atoms making up the crystal are arranged in a periodic fashion. That is, there is some basic arrangement of atoms that is repeated throughout the entire solid. Thus the crystal appears exactly the same at one point as it does at a series of other equivalent points, once the basic periodicity is discovered. However, not all solids are crystals (Fig. 1–1); some have no periodic structure at all (*amorphous* solids), and others are composed of many small regions of single-crystal material (*polycrystalline* solids). The high-resolution micrograph shown in Fig. 6–33 illustrates the periodic array of atoms in the single-crystal silicon of a transistor channel compared with the amorphous SiO<sub>2</sub> (glass) of the oxide layer.

1.2 CRYSTAL LATTICES

$<sup>^{1}</sup>$ The conversion between the energy E of a photon of light (eV) and its wavelength  $\lambda$  ( $\mu$ m) is  $\lambda=1.24/E$ . For GaAs,  $\lambda=1.24/1.43=0.87~\mu$ m.

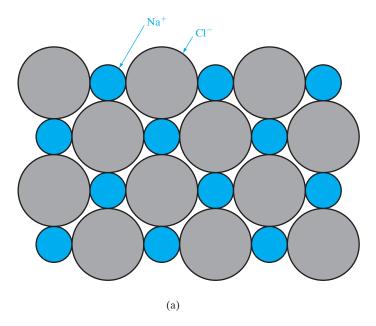

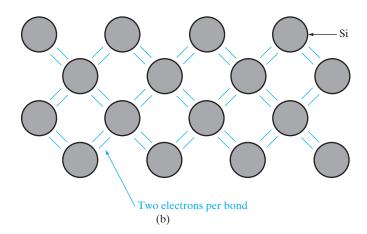

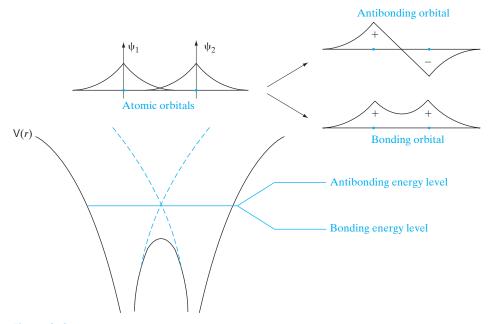

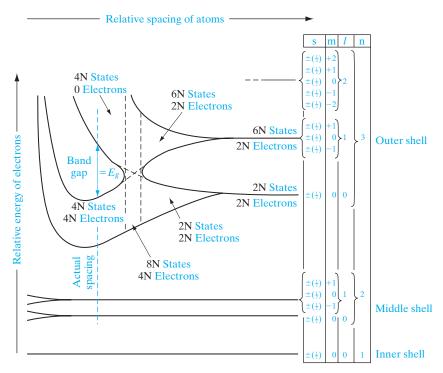

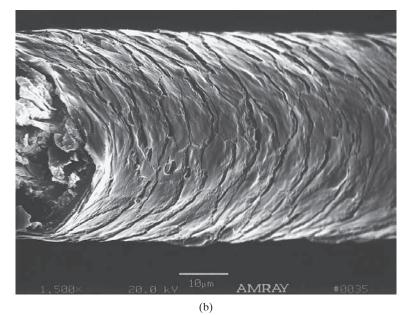

Figure 1-1 Three types of solids, classified according to atomic arrangement: (a) crystalline and (b) amorphous

materials are illustrated by microscopic views of the atoms, whereas (c) polycrystalline structure is illustrated by a more macroscopic view of adjacent single-crystalline regions, such as (a).

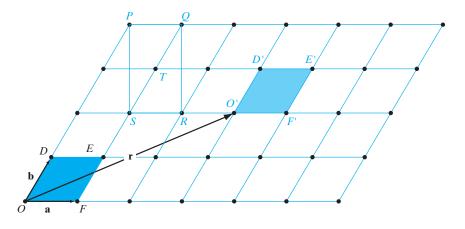

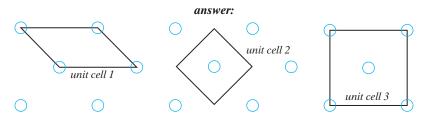

> The periodicity in a crystal is defined in terms of a symmetric array of points in space called the *lattice*. We can add atoms at each lattice point in an arrangement called a basis, which can be one atom or a group of atoms having the same spatial arrangement, to get a *crystal*. In every case, the lattice contains a volume or *cell* that represents the entire lattice and is regularly repeated throughout the crystal. As an example of such a lattice, Fig. 1–2 shows a two-dimensional arrangement of atoms called a rhombic lattice, with a primitive cell ODEF, which is the smallest such cell. Notice that we can define vectors **a** and **b** such that if the primitive cell is translated by integral multiples of these vectors, a new primitive cell identical to the original is found (e.g., O'D'E'F'). These vectors, **a** and **b** (and **c** if the lattice is three dimensional), are called the *primitive vectors* for the lattice. Points within the lattice are indistinguishable if the vector between the points is

$$\mathbf{r} = p\mathbf{a} + q\mathbf{b} + s\mathbf{c} \tag{1-1}$$

where p, q, and s are integers. The primitive cell shown has lattice points only at the corners of the cell. The primitive cell is not unique, but it must cover

Figure 1-2 A two-dimensional lattice showing translation of a unit cell by r = 3a + 2b.

the entire volume of the crystal (without missing or extra bits) by translations by integer numbers of primitive vectors, and it can have *only* one lattice point per cell. The convention is to choose the smallest primitive vectors. Note that, in the primitive cell shown in Fig. 1–2, the lattice points at the corners are shared with adjacent cells; thus, the effective number of lattice points belonging to the primitive cell is unity. Since there are many different ways of placing atoms in a volume, the distances and orientation between atoms can take many forms, leading to different lattice and crystal structures. It is important to remember that the symmetry determines the lattice, not the magnitudes of the distances between the lattice points.

In many lattices, however, the primitive cell is not the most convenient to work with. For example, in Fig. 1–2, we see that the rhombic arrangement of the lattice points is such that it can also be considered to be rectangular (PQRS) with a lattice point in the center at T (a so-called centered rectangular lattice). (Note that this is not true of all rhombic lattices!) Clearly, it is simpler to deal with a rectangle rather than a rhombus. So, in this case we can choose to work with a larger rectangular unit cell, PQRS, rather than the smallest primitive cell, ODEF. A unit cell allows lattice points not only at the corners but also at the face center (and body center in 3-D) if necessary. It is sometimes used instead of the primitive cell if it can represent the symmetry of the lattice better (in this example "centered rectangular" two-dimensional lattice). It replicates the lattice by integer translations of basis vectors.

The importance of the unit cell lies in the fact that we can analyze the crystal as a whole by investigating a representative volume. For example, from the unit cell we can find the distances between nearest atoms and next nearest atoms for calculation of the forces holding the lattice together; we can look at the fraction of the unit cell volume filled by atoms and relate the density of the solid to the atomic arrangement. But even more important for our interest in electronic devices, the properties of the periodic crystal lattice determine the allowed energies of electrons that participate in the conduction process. Thus the lattice determines not only the mechanical properties of the crystal but also its electrical properties.

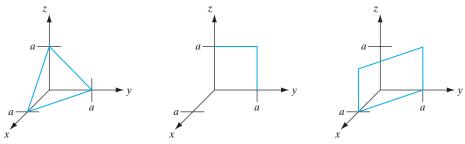

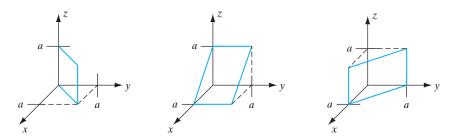

#### 1.2.2 **Cubic Lattices**

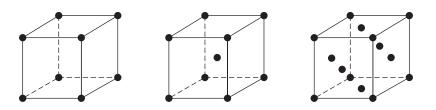

The simplest three-dimensional lattice is one in which the unit cell is a cubic volume, such as the three cells shown in Fig. 1–3. The *simple cubic* structure (abbreviated sc) has an atom located at each corner of the unit cell. The

Simple cubic

Body-centered cubic

Face-centered cubic

Figure 1-3 Unit cells for three types of cubic lattice structures.

Figure 1–4

Packing of hard

spheres in an fcc

lattice.

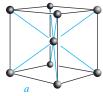

body-centered cubic (bcc) lattice has an additional atom at the center of the cube, and the face-centered cubic (fcc) unit cell has atoms at the eight corners and centered on the six faces. All three structures have different primitive cells, but the same cubic unit cell. We will generally work with unit cells.

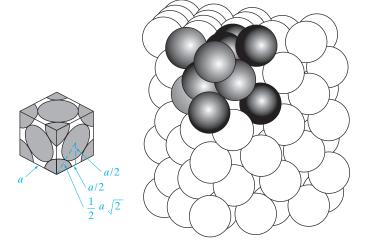

As atoms are packed into the lattice in any of these arrangements, the distances between neighboring atoms will be determined by a balance between the forces that attract them together and other forces that hold them apart. We shall discuss the nature of these forces for particular solids in Section 3.1.1. For now, we can calculate the maximum fraction of the lattice volume that can be filled with atoms by approximating the atoms as hard spheres. For example, Fig. 1–4 illustrates the packing of spheres in a fcc cell of side a, such that the nearest neighbors touch. The dimension a for a cubic unit cell is called the *lattice constant*. For the fcc lattice the nearest neighbor distance is one-half the diagonal of a face, or  $\frac{1}{2}(a\sqrt{2})$ . Therefore, for the atom centered on the face to just touch the atoms at each corner of the face, the radius of the sphere must be one-half the nearest neighbor distance, or  $\frac{1}{4}(a\sqrt{2})$ .

**EXAMPLE 1–1** Find the fraction of the fcc unit cell volume filled with hard spheres.

SOLUTION Nearest atom separation =

$$\frac{5\sqrt{2}}{2}$$

Å = 3.54 Å

Tetrahedral radius = 1.77 Å

Volume of each atom = 23.14 Å<sup>3</sup>

Number of atoms per cube  $6 \cdot \frac{1}{2} + 8 \cdot \frac{1}{8} = 4$  atoms

Packing fraction  $\frac{23.1 \text{ Å}^3 \cdot 4}{(5 \text{ Å})^3} = 0.74 = 74\%$

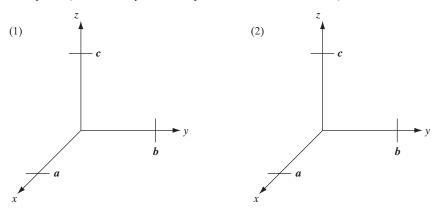

#### 1.2.3 Planes and Directions

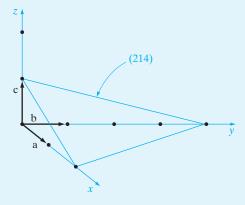

In discussing crystals it is very helpful to be able to refer to planes and directions within the lattice. The notation system generally adopted uses a set of three integers to describe the position of a plane or the direction of a vector within the lattice. We first set up an xyz coordinate system with the origin at any lattice point (it does not matter which one because they are all equivalent!), and the axes are lined up with the edges of the cubic unit cell. The three integers describing a particular plane are found in the following way:

- 1. Find the intercepts of the plane with the crystal axes and express these intercepts as integral multiples of the basis vectors (the plane can be moved in and out from the origin, retaining its orientation, until such an integral intercept is discovered on each axis).

- 2. Take the reciprocals of the three integers found in step 1 and reduce these to the smallest set of integers *h*, *k*, and *l*, which have the same relationship to each other as the three reciprocals.

- 3. Label the plane (hkl).

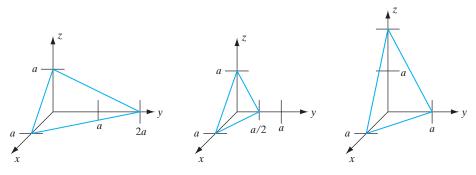

The plane illustrated in Fig. 1–5 has intercepts at  $2\mathbf{a}$ ,  $4\mathbf{b}$ , and  $1\mathbf{c}$  along the three crystal axes. Taking the reciprocals of these intercepts, we get  $\frac{1}{2}$ ,  $\frac{1}{4}$ , and 1. These three fractions have the same relationship to each other as the integers 2, 1, and 4 (obtained by multiplying each fraction by 4). Thus the plane can be referred to as a (214) plane. The only exception is if the intercept is a fraction of the lattice constant a. In that case, we do not reduce it to the lowest set of integers. For example, in Fig. 1–3, planes parallel to the cube faces, but going through the body center atoms in the bcc lattice, would be (200) and not (100).

EXAMPLE 1-2

Figure 1–5 A (214) crystal plane.

The three integers h, k, and l are called the *Miller indices*; these three numbers define a set of parallel planes in the lattice. One advantage of taking the reciprocals of the intercepts is avoidance of infinities in the notation. One

intercept is infinity for a plane parallel to an axis; however, the reciprocal of such an intercept is taken as zero. If a plane contains one of the axes, it is parallel to that axis and has a zero reciprocal intercept. If a plane passes through the origin, it can be translated to a parallel position for calculation of the Miller indices. If an intercept occurs on the negative branch of an axis, the minus sign is placed above the Miller index for convenience, such as  $(h\bar{k}l)$ .

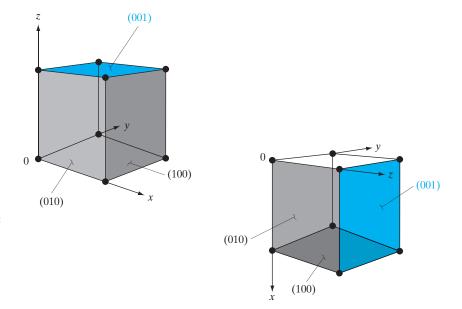

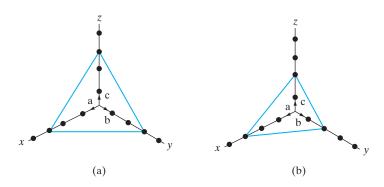

From a crystallographic point of view, many planes in a lattice are equivalent; that is, a plane with given Miller indices can be shifted about in the lattice simply by choice of the position and orientation of the unit cell. The indices of such equivalent planes are enclosed in braces {} instead of parentheses. For example, in the cubic lattice of Fig. 1–6, all the cube faces are crystallographically equivalent in that the unit cell can be rotated in various directions and still appear the same. The six equivalent faces are collectively designated as {100}.

A direction in a lattice is expressed as a set of three integers with the same relationship as the components of a vector in that direction. The three vector components are expressed in multiples of the basis vectors, and the three integers are reduced to their smallest values while retaining the relationship among them. For example, the body diagonal in the cubic lattice (Fig. 1–7a) is composed of the components 1a, 1b, and 1c; therefore, this diagonal is the [111] direction. (Brackets are used for direction indices.) As in the case of planes, many directions in a lattice are equivalent, depending only on the arbitrary choice of orientation for the axes. Such equivalent direction indices are placed in angular brackets  $\langle \ \rangle$ . For example, the crystal axes in the cubic lattice [100], [010], and [001] are all equivalent and are called  $\langle 100 \rangle$  directions (Fig. 1–7b).

Figure 1-6

Equivalence of the cube faces ({100} planes) by rotation of the unit cell within the cubic lattice.

Figure 1–7

Crystal directions in the cubic lattice.

Two useful relationships in terms of Miller indices describe the distance between planes and angles between directions. The distance d between two adjacent planes labeled (hkl) is given in terms of the lattice constant, a, as

$$d = a/(h^2 + k^2 + l^2)^{1/2} (1-2a)$$

The angle  $\theta$  between two different Miller index directions is given by

$$\cos \theta = \{h_1 h_2 + k_1 k_2 + l_1 l_2\} \{(h_1^2 + k_1^2 + l_1^2)^{1/2} (h_2^2 + k_2^2 + l_2^2)^{1/2}\}$$

(1-2b)

Comparing Figs. 1–6 and 1–7, we notice that in cubic lattices a direction [hkl] is perpendicular to the plane (hkl). This is convenient in analyzing lattices with cubic unit cells, but it should be remembered that it is not necessarily true in noncubic systems.

#### 1.2.4 The Diamond Lattice

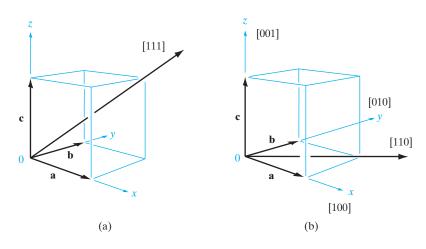

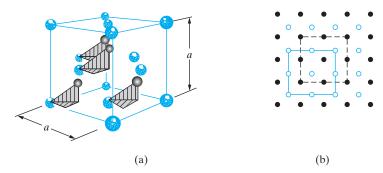

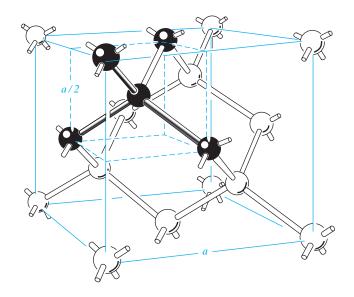

The basic crystal structure for many important semiconductors is the fcc lattice with a basis of two atoms, giving rise to the *diamond* structure, characteristic of Si, Ge, and C in the diamond form. In many compound semiconductors, atoms are arranged in a basic diamond structure, but are different on alternating sites. This is called a *zinc blende* structure and is typical of the III–V compounds. One of the simplest ways of stating the construction of the diamond structure is the following:

The diamond structure can be thought of as an fcc lattice with an extra atom placed at  $\mathbf{a}/4 + \mathbf{b}/4 + \mathbf{c}/4$  from each of the fcc atoms.

Figure 1–8a illustrates the construction of a diamond lattice from an fcc unit cell. We notice that when the vectors are drawn with components one-fourth of the cube edge in each direction, only four additional points within the same unit cell are reached. Vectors drawn from any of the other fcc atoms simply determine corresponding points in adjacent unit cells. This method of

Figure 1–8

Diamond lattice structure: (a) a unit cell of the diamond lattice constructed by placing atoms  $\frac{1}{4}$ ,  $\frac{1}{4}$ ,  $\frac{1}{4}$  from each atom in an fcc; (b) top view (along any  $\langle 100 \rangle$  direction) of an extended diamond lattice. The colored circles indicate one fcc sublattice and the black circles indicate the interpenetrating fcc.

constructing the diamond lattice implies that the original fcc has associated with it a second interpenetrating fcc displaced by  $\frac{1}{4}$ ,  $\frac{1}{4}$ ,  $\frac{1}{4}$ . The two interpenetrating fcc *sublattices* can be visualized by looking down on the unit cell of Fig. 1–8a from the top (or along any  $\langle 100 \rangle$  direction). In the top view of Fig. 1–8b, atoms belonging to the original fcc are represented by open circles, and the interpenetrating sublattice is shaded. If the atoms are all similar, we call this structure a diamond lattice; if the atoms differ on alternating sites, it is a zinc blende structure. For example, if one fcc sublattice is composed of Ga atoms and the interpenetrating sublattice is As, the zinc blende structure of GaAs results. Most of the compound semiconductors have this type of lattice, although some of the II–VI compounds are arranged in a slightly different structure called the *wurtzite* lattice. We shall restrict our discussion here to the diamond and zinc blende structures, since they are typical of most of the commonly used semiconductors.

# EXAMPLE 1-3 Calculate the volume density of Si atoms (number of atoms/cm³), given that the lattice constant of Si is 5.43 Å. Calculate the areal density of atoms (number/cm²) on the (100) plane.

**SOLUTION** On the (100) plane, we have four atoms on corners and one on the face center.

(100) plane:

$$\frac{4 \times \frac{1}{4} + 1}{(5.43 \times 10^{-8})(5.43 \times 10^{-8})} = 6.8 \times 10^{14} \text{cm}^{-2}$$

For Si, we have eight corner lattice points, six face centered points, and two atoms

Number of atoms per cube =

$$(8 \times \frac{1}{8} + \frac{1}{2} \times 6) \times 2 = 8$$

Volume density =

$$\frac{8}{(5.43 \times 10^{-8})^3}$$

=  $5.00 \times 10^{22}$  cm<sup>-3</sup>

A particularly interesting and useful feature of the III–V compounds is the ability to vary the mixture of elements on each of the two interpenetrating fcc sublattices of the zinc blende crystal. For example, in the ternary compound AlGaAs, it is possible to vary the composition of the ternary alloy by choosing the fraction of Al or Ga atoms on the column III sublattice. It is common to represent the composition by assigning subscripts to the various elements. For example, Al<sub>x</sub>Ga<sub>1-x</sub>As refers to a ternary alloy in which the column III sublattice in the zinc blende structure contains a fraction x of Al atoms and 1-x of Ga atoms. The composition Al<sub>0.3</sub>Ga<sub>0.7</sub>As has 30 percent Al and 70 percent Ga on the column III sites, with the interpenetrating column V sublattice occupied entirely by As atoms. It is extremely useful to be able to grow ternary alloy crystals such as this with a given composition. For the Al<sub>r</sub>Ga<sub>1-r</sub>As example we can grow crystals over the entire composition range from x = 0 to x = 1, thus varying the electronic and optical properties of the material from that of GaAs (x = 0) to that of AlAs (x = 1). To vary the properties even further, it is possible to grow four-element (quaternary) compounds such as  $In_xGa_{1-x}As_vP_{1-v}$  having a very wide range of properties.

It is important from an electronic point of view to notice that each atom in the diamond and zinc blende structures is surrounded by four nearest neighbors (Fig. 1–9). The importance of this relationship of each atom to its neighbors will become evident in Section 3.1.1 when we discuss the bonding forces which hold the lattice together.

The fact that atoms in a crystal are arranged in certain planes is important to many of the mechanical, metallurgical, and chemical properties of the material. For example, crystals often can be cleaved along certain atomic planes, resulting in exceptionally planar surfaces. This is a familiar result in cleaved diamonds for jewelry; the facets of a diamond reveal clearly the triangular, hexagonal, and rectangular symmetries of intersecting planes in various crystallographic directions. Semiconductors with diamond and zinc blende lattices have similar cleavage planes. Chemical reactions, such as etching of the crystal, often take place preferentially along certain directions. These properties serve as interesting illustrations of crystal symmetry, but in addition, each plays an important role in fabrication processes for many semiconductor devices.

Figure 1-9

Diamond

lattice unit cell,

showing the four

nearest neighbor

structure. (From

Electrons and Holes

in Semiconductors

by W. Shockley,

© 1950 by Litton

Educational

Publishing Co.,

Inc.; by permission

of Van Nostrand

Reinhold Co., Inc.)

#### 1.3 BULK CRYSTAL GROWTH

The progress of solid state device technology since the invention of the transistor in 1948 has depended not only on the development of device concepts but also on the improvement of materials. For example, the fact that ICs can be made today is the result of a considerable breakthrough in the growth of pure, single-crystal Si in the early and mid-1950s. The requirements on the growing of device-grade semiconductor crystals are more stringent than those for any other materials. Not only must semiconductors be available in large single crystals, but also the purity must be controlled within extremely close limits. For example, Si crystals now being used in devices are grown with concentrations of most impurities of less than one part in ten billion. Such purities require careful handling and treatment of the material at each step of the manufacturing process.

#### 1.3.1 Starting Materials

The raw feedstock for Si crystal is silicon dioxide (SiO<sub>2</sub>). We react SiO<sub>2</sub> with C in the form of coke in an arc furnace at very high temperatures ( $\sim$ 1800°C) to reduce SiO<sub>2</sub> according to the following reaction:

$$SiO_2 + 2C \rightarrow Si + 2CO$$

(1–3)

This forms metallurgical grade Si (MGS) which has impurities such as Fe, Al, and heavy metals at levels of several hundred to several thousand parts per million (ppm). Refer back to Example 1–3 to see that 1 ppm of Si corresponds to an impurity level of  $5 \times 10^{16} \, \mathrm{cm}^{-3}$ . While MGS is clean enough for metallurgical applications such as using Si to make stainless steel, it is not pure enough for electronic applications; it is also not single crystal.

The MGS is refined further to yield semiconductor-grade or electronic-grade Si (EGS), in which the levels of impurities are reduced to parts per billion or ppb (1 ppb =  $5 \times 10^{13} \, \text{cm}^{-3}$ ). This involves reacting the MGS with dry HCl according to the following reaction to form trichlorosilane, SiHCl<sub>3</sub>, which is a liquid with a boiling point of 32°C:

$$Si + 3HCl \rightarrow SiHCl_3 + H_2$$

(1-4)

Along with SiHCl<sub>3</sub>, chlorides of impurities such as FeCl<sub>3</sub> are formed which fortunately have boiling points that are different from that of SiHCl<sub>3</sub>. This allows a technique called fractional distillation to be used, in which we heat up the mixture of SiHCl<sub>3</sub> and the impurity chlorides, and condense the vapors in different distillation towers held at appropriate temperatures. We can thereby separate pure SiHCl<sub>3</sub> from the impurities. SiHCl<sub>3</sub> is then converted to highly pure EGS by reaction with  $H_2$ ,

$$2SiHCl3 + 2H2 \rightarrow 2Si + 6HCl$$

(1–5)

#### 1.3.2 Growth of Single-Crystal Ingots

Next, we have to convert the high purity but still polycrystalline EGS to single-crystal Si ingots or boules. This is generally done today by a process commonly called the *Czochralski* method. In order to grow single-crystal material, it is necessary to have a seed crystal which can provide a template for growth. We melt the EGS in a quartz-lined graphite crucible by resistively heating it to the melting point of Si (1412°C).

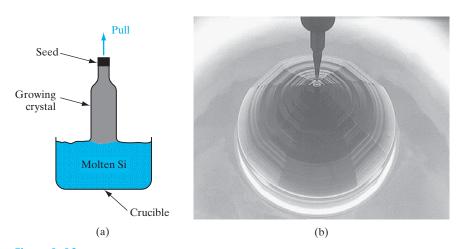

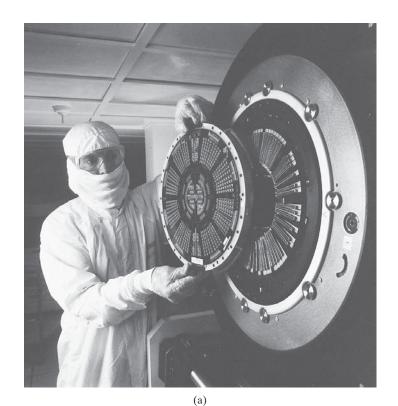

A seed crystal is lowered into the molten material and then is raised slowly, allowing the crystal to grow onto the seed (Fig. 1–10a). Generally, the

Figure 1–10 Pulling of a Si crystal from the melt (Czochralski method): (a) schematic diagram of the crystal growth process; (b) an 8-in. diameter,  $\langle$  100 $\rangle$  oriented Si crystal being pulled from the melt. (Photograph courtesy of MEMC Electronics Intl.)

(a)

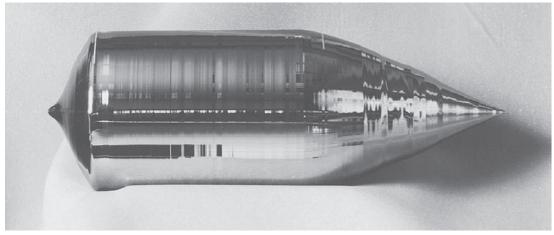

Figure 1-11

(a) Silicon crystal grown by the Czochralski method. This large single-crystal ingot provides 300 mm (12-in.) diameter wafers when sliced using a saw. The ingot is about 1.0 m long (including the tapered regions), and weighs about 140 kg. (b) technician holding a 300 mm wafer. (Photograph courtesy of MEMC Electronics Intl.)

crystal is rotated slowly as it grows to provide a slight stirring of the melt and to average out any temperature variations that would cause inhomogeneous solidification. This technique is widely used in growing Si, Ge, and some of the compound semiconductors.

In pulling compounds such as GaAs from the melt, it is necessary to prevent volatile elements (e.g., As) from vaporizing. In one method a layer of  $B_2O_3$ , which is dense and viscous when molten, floats on the surface of the molten GaAs to prevent As evaporation. This growth method is called *liquid-encapsulated Czochralski* (*LEC*) growth.

In Czochralski crystal growth, the shape of the ingot is determined by a combination of the tendency of the cross section to assume a polygonal shape due to the crystal structure and the influence of surface tension, which encourages a circular cross section. The crystal facets are noticeable in the initial growth near the seed crystal in Fig. 1–10b. However, the cross section of the large ingot in Fig. 1–11 is almost circular.

In the fabrication of Si ICs (Chapter 9) it is economical to use very large Si wafers, so that many IC chips can be made simultaneously. As a result, considerable research and development have gone into methods for growing very large Si crystals. For example, Fig. 1–11 illustrates a ~12-inch or 300-mm diameter Si ingot, 1.0 m long and weighing 140 kg, and a 300 mm wafer.

#### 1.3.3 Wafers

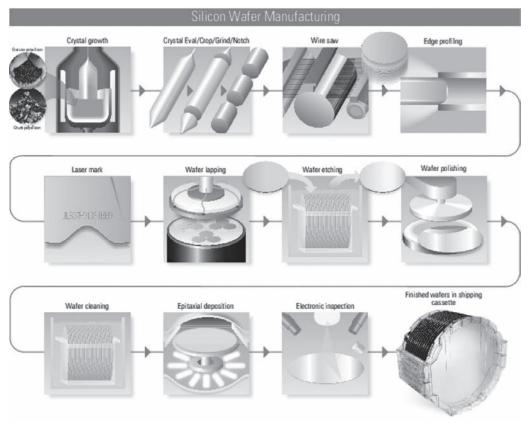

After the single-crystal ingot is grown, it is then mechanically processed to manufacture wafers. The first step involves mechanically grinding the more-or-less cylindrical ingot into a perfect cylinder with a precisely controlled diameter. This is important because in a modern IC fabrication facility, many processing tools and wafer handling robots require tight tolerances on the size of the wafers. Using X-ray crystallography, crystal planes in the ingot are identified. For reasons discussed in Section 6.4.3, most Si ingots are grown along the  $\langle 100 \rangle$  direction (Fig. 1–10). For such ingots, a small notch is ground on one side of the cylinder to delineate a  $\{110\}$  face of the crystal. This is useful because for  $\langle 100 \rangle$  Si wafers, the  $\{110\}$  cleavage planes are orthogonal to each other. This notch then allows the individual IC chips to be made oriented along  $\{110\}$  planes so that when the chips are sawed apart, there is less chance of spurious cleavage of the crystal, which could cause good chips to be lost.

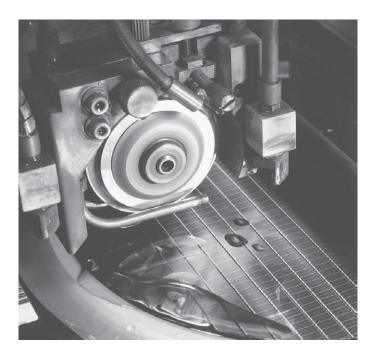

Next, the Si cylinder is sawed into individual wafers about 775  $\mu$ m thick, by using a diamond-tipped inner-hole blade saw, or a wire saw (Fig. 1–12). State-of-the-art wafers today are 300 mm in diameter; the next size will be 450 mm. The resulting wafers are mechanically lapped and ground on both sides to achieve a flat surface, and to remove the mechanical damage due to sawing. Such damage would have a detrimental effect on devices. The flatness of the wafer is critical from the point of view of "depth of focus" or how sharp an image can be focussed on the wafer surface during photolithography, as discussed in Chapter 5. The Si wafers are then rounded or "chamfered" along the edges to minimize the likelihood of chipping the wafers during processing. Finally, the wafers undergo chemical–mechanical

Figure 1–12

Steps involved in manufacturing Si wafers. (Photograph courtesy of MEMC Electronics Intl.)

polishing using a slurry of very fine SiO<sub>2</sub> particles in a basic NaOH solution to give the front surface of the wafer a mirror-like finish. The wafers are now ready for IC fabrication (Fig. 1–12). The economic value added in this process is impressive. From sand (SiO<sub>2</sub>) costing pennies, we can obtain Si wafers costing a few hundred dollars, on which we can make hundreds of microprocessors, for example, each costing several hundred dollars.

# 1.3.4 Doping

As previously mentioned, there are some impurities in the molten EGS. We may also add intentional impurities or dopants to the Si melt to change its electronic properties. At the solidifying interface between the melt and the solid, there will be a certain distribution of impurities between the two phases. An important quantity that identifies this property is the *distribution coefficient*  $k_d$ , which is the ratio of the concentration of the impurity in the solid  $C_S$  to the concentration in the liquid  $C_L$  at equilibrium:

$$k_d = \frac{C_S}{C_I} \tag{1-6}$$

The distribution coefficient is a function of the material, the impurity, the temperature of the solid–liquid interface, and the growth rate. For an impurity with a distribution coefficient of one-half, the relative concentration of the impurity in the molten liquid to that in the refreezing solid is two to one. Thus the concentration of impurities in that portion of material that solidifies first is one-half the original concentration  $C_0$ . The distribution coefficient is thus important during growth from a melt. This can be illustrated by an example involving Czochralski growth:

Find the weight of As  $(k_d = 0.3)$  added to 1 kg Si in Czochralski growth for  $10^{15}$  cm<sup>-3</sup> doping.

**EXAMPLE 1-4**

atomic weight of As =  $74.9 \frac{g}{\text{mol}}$

SOLUTION

$$C_s = k_d \cdot C_L = 10^{15} \frac{1}{\text{cm}^3} \rightarrow C_L \frac{10^{15} \frac{1}{\text{cm}^3}}{0.3} = 3.33 \cdot 10^{15} \frac{1}{\text{cm}^3}$$

Assume As may be neglected for overall melt weight and volume

$$\frac{1000g \text{ Si}}{2.33 \frac{g}{\text{cm}^3}} = 429.2 \text{ cm}^3 \text{ Si}$$

$$3.33 \cdot 10^{15} \frac{1}{\text{cm}^3} \cdot 429.2 \text{ cm}^3 = 1.43 \cdot 10^{18} \text{ As atoms}$$

$$\frac{1.43 \cdot 10^{18} \text{ atoms} \cdot 74.9 \frac{g}{\text{mol}}}{6.02 \cdot 10^{23} \frac{\text{atoms}}{\text{mol}}} = 1.8 \cdot 10^{-4} \text{g As} = 1.8 \cdot 10^{-7} \text{kg As}$$

One of the most important and versatile methods of crystal growth for device applications is the growth of a thin crystal layer on a wafer of a compatible crystal. The substrate crystal may be a wafer of the same material as the grown layer or a different material with a similar lattice structure. In this process the substrate serves as the seed crystal onto which the new crystalline material grows. The growing crystal layer maintains the crystal structure and orientation of the substrate. The technique of growing an oriented single-crystal layer on a substrate wafer is called *epitaxial growth*, or *epitaxy*. As we shall see in this section, epitaxial growth can be performed at temperatures considerably below the melting point of the substrate crystal. A variety of methods are used to provide the appropriate atoms to the surface of the growing layer. These methods include *chemical vapor deposition* (CVD),<sup>2</sup>

1.4 EPITAXIAL GROWTH

<sup>&</sup>lt;sup>2</sup>The generic term *chemical vapor deposition* includes the deposition of layers that may be polycrystalline or amorphous. When a CVD process results in a single-crystal epitaxial layer, a more specific term is *vapor-phase epitaxy* (VPE).

growth from a melt (*liquid-phase epitaxy*, *LPE*), and evaporation of the elements in a vacuum (*molecular beam epitaxy*, *MBE*). With this wide range of epitaxial growth techniques, it is possible to grow a variety of crystals for device applications, having properties specifically designed for the electronic or optoelectronic device being made.

## 1.4.1 Lattice-Matching in Epitaxial Growth

When Si epitaxial layers are grown on Si substrates, there is a natural matching of the crystal lattice, and high-quality single-crystal layers result. On the other hand, it is often desirable to obtain epitaxial layers that differ somewhat from the substrate, which is known as *heteroepitaxy*. This can be accomplished easily if the lattice structure and lattice constant *a* match for the two materials. For example, GaAs and AlAs both have the zinc blende structure, with a lattice constant of about 5.65 Å. As a result, epitaxial layers of the ternary alloy AlGaAs can be grown on GaAs substrates with little lattice mismatch. Similarly, GaAs can be grown on Ge substrates (see Appendix III).

Since AlAs and GaAs have similar lattice constants, it is also true that the ternary alloy AlGaAs has essentially the same lattice constant over the entire range of compositions from AlAs to GaAs. As a result, one can choose the composition x of the ternary compound  $Al_xGa_{1-x}As$  to fit the particular device requirement, and grow this composition on a GaAs wafer. The resulting epitaxial layer will be lattice-matched to the GaAs substrate.

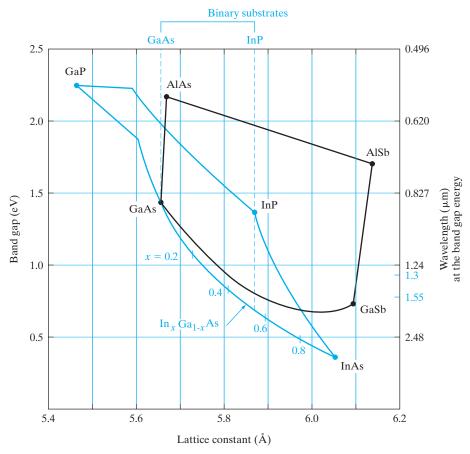

Figure 1–13 illustrates the energy band gap  $E_g$  as a function of lattice constant a for several III–V ternary compounds as they are varied over their composition ranges. For example, as the ternary compound InGaAs is varied by choice of composition on the column III sublattice from InAs to GaAs, the band gap changes from 0.36 to 1.43 eV while the lattice constant of the crystal varies from 6.06 Å for InAs to 5.65 Å for GaAs. Clearly, we cannot grow this ternary compound over the entire composition range on a particular binary substrate, which has a fixed lattice constant. As Fig. 1–13 illustrates, however, it is possible to grow a specific composition of InGaAs on an InP substrate. The vertical (invariant lattice constant) line from InP to the InGaAs curve shows that a midrange ternary composition (actually, In<sub>0.53</sub>Ga<sub>0.47</sub>As) can be grown lattice-matched to an InP substrate. Similarly, a ternary InGaP alloy with about 50 percent Ga and 50 percent In on the column III sublattice can be grown lattice-matched to a GaAs substrate. To achieve a broader range of alloy compositions, grown lattice-matched on particular substrates, it is helpful to use quaternary alloys such as InGaAsP. The variation of compositions on both the column III and column V sublattices provides additional flexibility in choosing a particular band gap while providing lattice-matching to convenient binary substrates such as GaAs or InP.

In the case of GaAsP, the lattice constant is intermediate between that of GaAs and GaP, depending upon the composition. For example, GaAsP crystals used in red LEDs have 40 percent phosphorus and 60 percent arsenic on the column V sublattice. Since such a crystal cannot be grown directly on

Figure 1–13

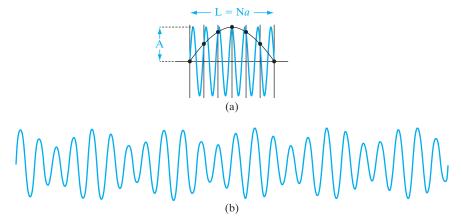

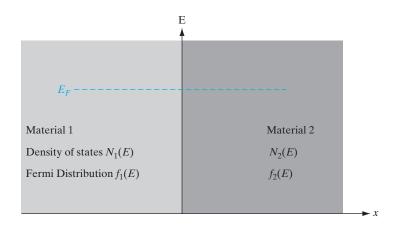

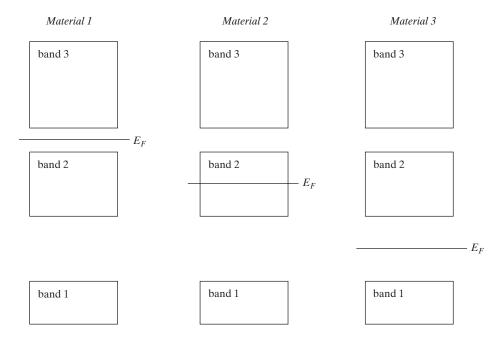

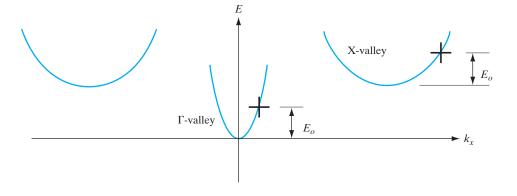

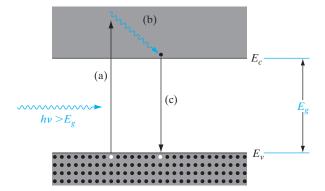

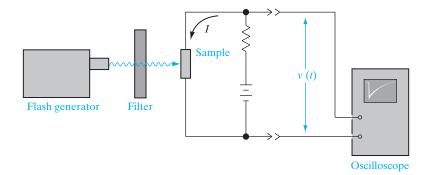

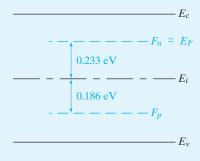

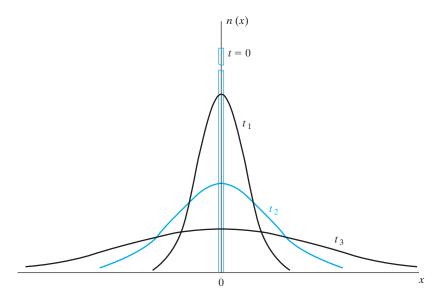

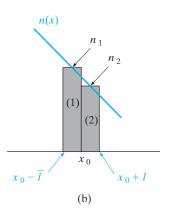

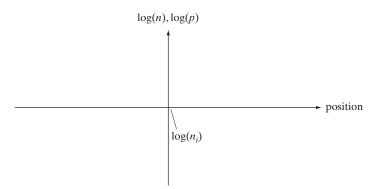

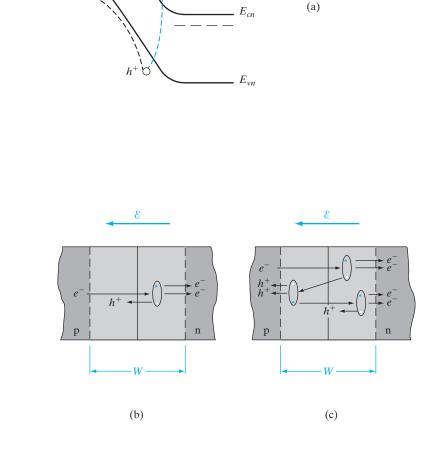

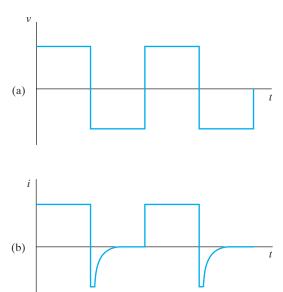

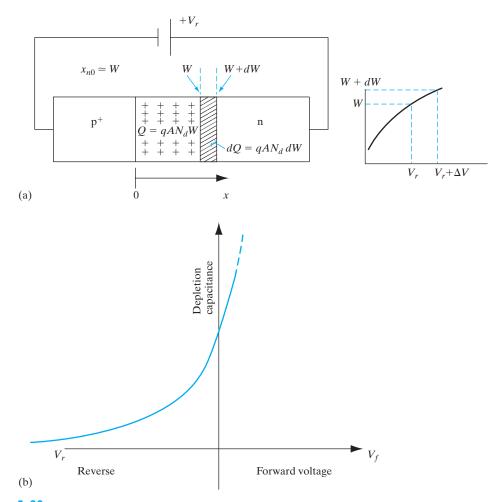

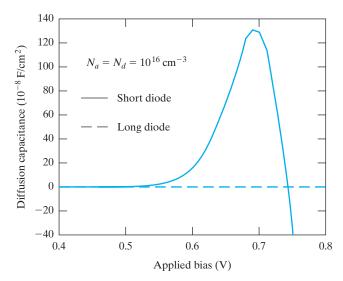

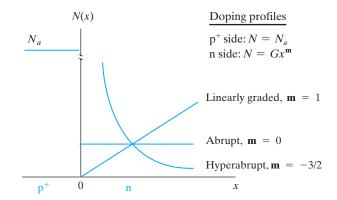

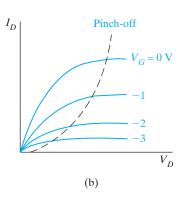

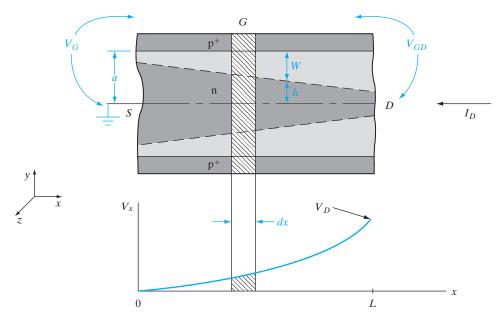

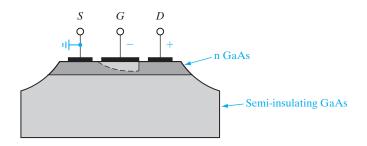

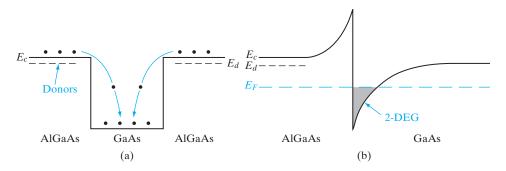

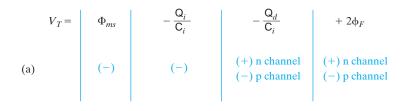

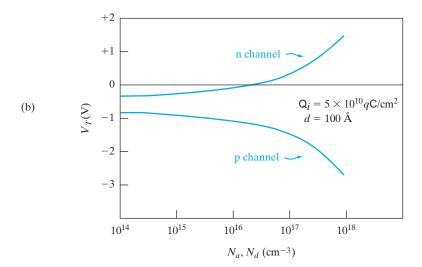

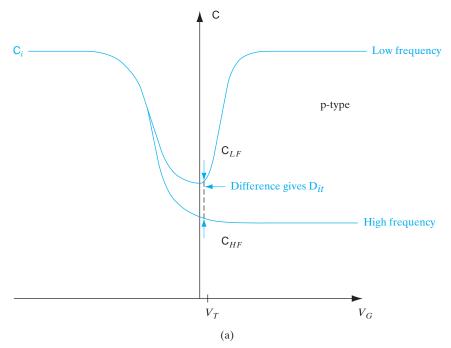

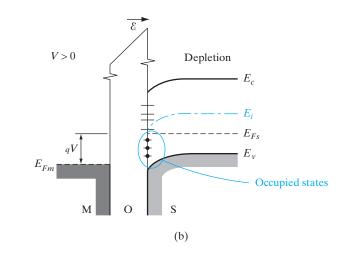

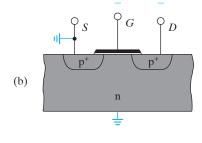

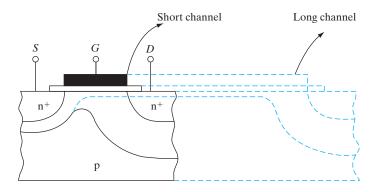

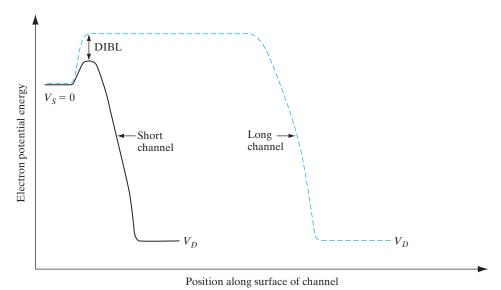

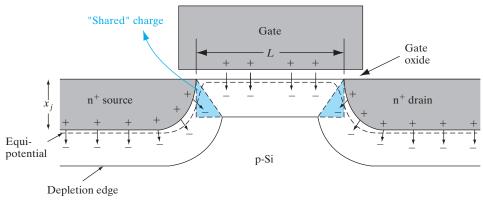

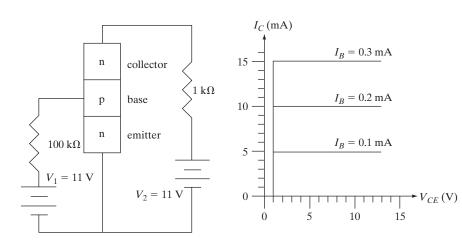

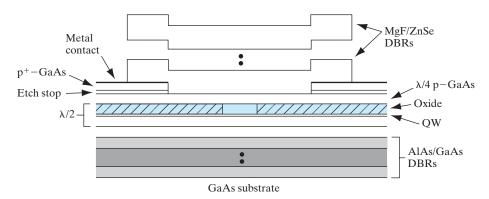

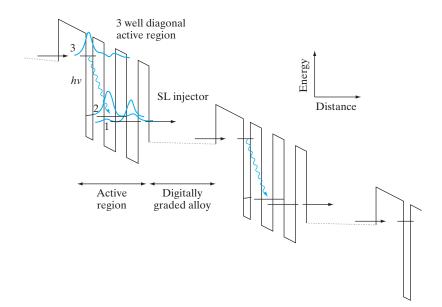

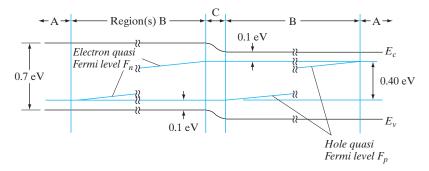

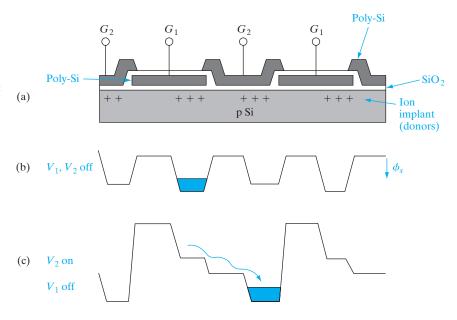

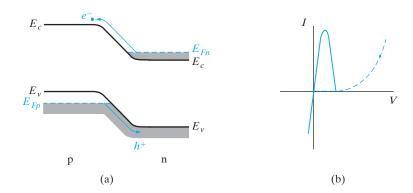

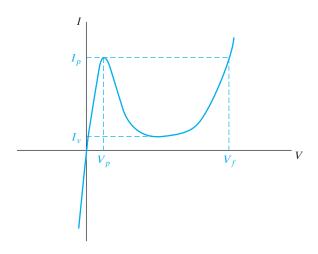

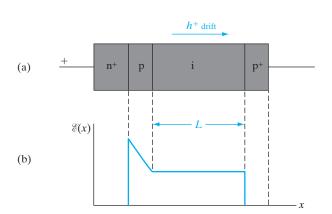

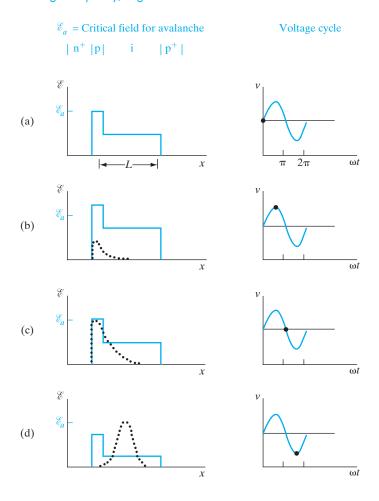

Relationship between band gap and lattice constant for alloys in the InGaAsP and AlGaAsSb systems. The dashed vertical lines show the lattice constants for the commercially available binary substrates GaAs and InP. For the marked example of  $\ln_x Ga_{1-x}As$ , the ternary composition x=0.53 can be grown lattice-matched on InP, since the lattice constants are the same. For quaternary alloys, the compositions on both the III and V sublattices can be varied to grow lattice-matched epitaxial layers along the dashed vertical lines between curves. For example,  $\ln_x Ga_{1-x}As_y P_{1-y}$  can be grown on InP substrates, with resulting band gaps ranging from 0.75 eV to 1.35 eV. In using this figure, assume the lattice constant a of a ternary alloy varies linearly with the composition x.